MF0ICU1001W(2010) Просмотр технического описания (PDF) - NXP Semiconductors.

Номер в каталоге

Компоненты Описание

производитель

MF0ICU1001W Datasheet PDF : 28 Pages

| |||

NXP Semiconductors

MF0ICU1

MIFARE Ultralight contactless single-ticket IC

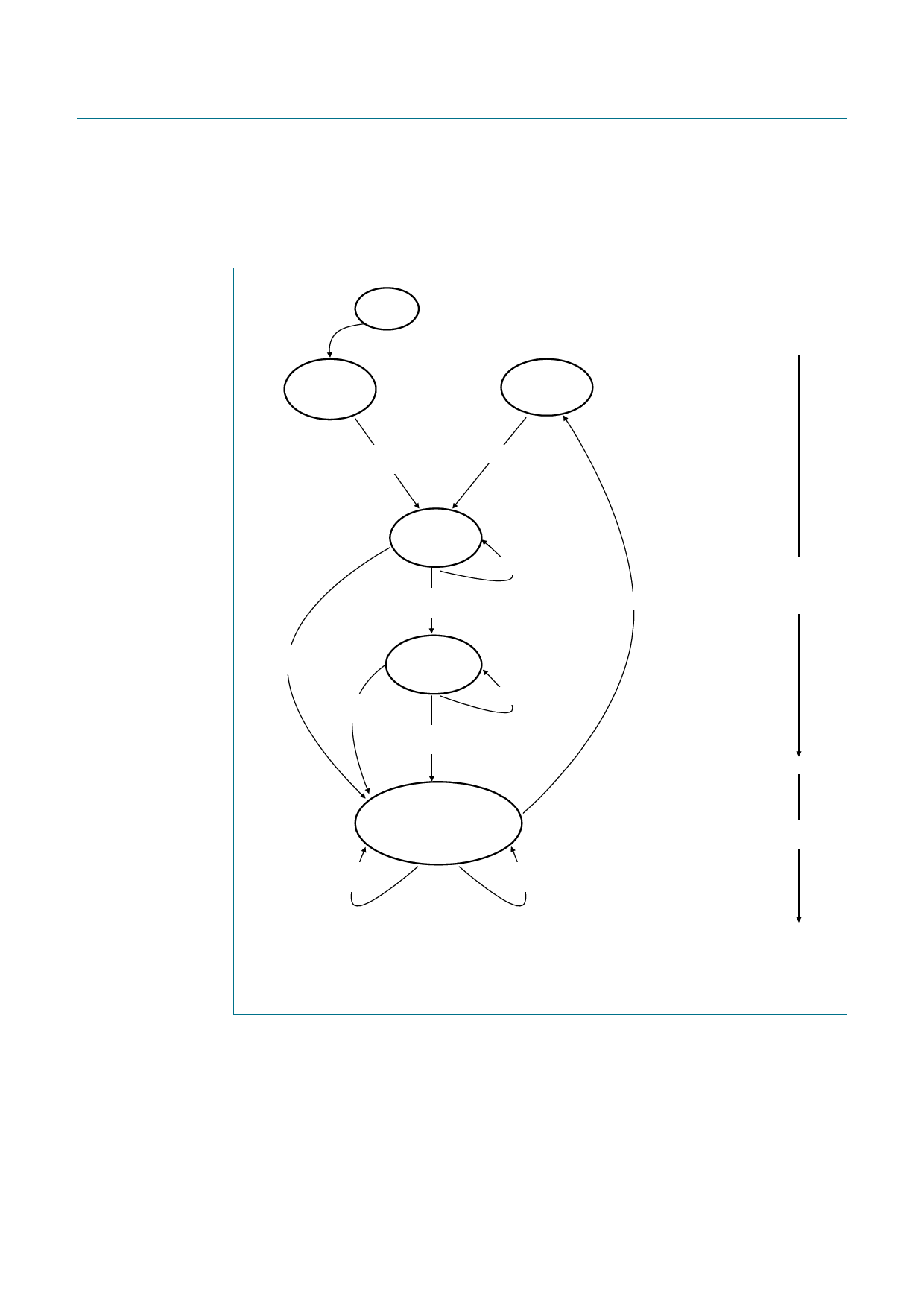

8. Functional description

8.1 Block description

The MF0ICU1 chip consists of a 512-bit EEPROM, RF interface and Digital Control Unit

(DCU). Energy and data are transferred via an antenna consisting of a coil with a small

number of turns which is directly connected to the MF0ICU1. No further external

components are necessary. Refer to the document Ref. 6 “MIFARE (Card) Coil Design

Guide” for details on antenna design.

• RF interface:

– Modulator/demodulator

– Rectifier

– Clock regenerator

– Power-On Reset (POR)

– Voltage regulator

• Anticollision: Multiple cards may be selected and managed in sequence

• Command interpreter: Processes commands supported by the MF0ICU1 to access

the memory

• EEPROM interface

• EEPROM: 512 bits, organized in 16 pages of 4 bytes per page.

– 80 bits reserved for manufacturer data

– 16 bits used for the read-only locking mechanism

– 32 bits available as OTP area

– 384 bits user programmable Read/Write memory

MF0ICU1

Product data sheet

PUBLIC

All information provided in this document is subject to legal disclaimers.

Rev. 3.8 — 22 December 2010

028638

© NXP B.V. 2010. All rights reserved.

7 of 28