FXAS21002CQR1 Просмотр технического описания (PDF) - NXP Semiconductors.

Номер в каталоге

Компоненты Описание

производитель

FXAS21002CQR1 Datasheet PDF : 58 Pages

| |||

Digital Interfaces

3.2.1 General SPI Operation

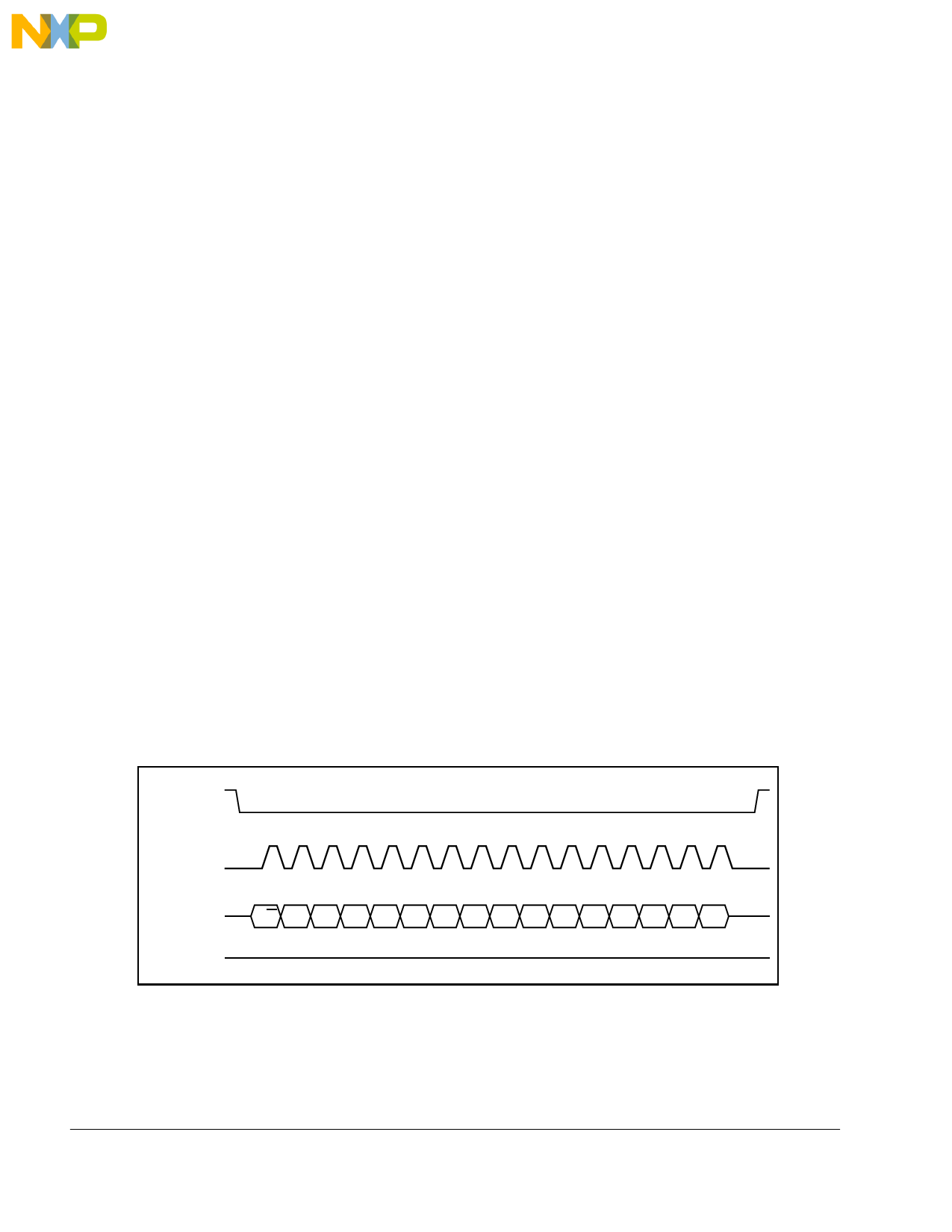

The SPI_CS_B pin is driven low at the start of a transaction, held low for the duration

of the transfer, and then driven high again after the transaction is completed. During a

transaction, the master toggles the clock (SCLK). The SCLK polarity is defined as

having an idle value that is low, and an active phase that is high (CPOL = 0). Serial

input and output data is captured on the clock's rising edge and propagated on the

falling edge (CPHA = 0). Single byte read and single byte write operations are

completed in 16 SCLK cycles; multiple byte reads and writes are completed in

additional multiples of 8 SCLK cycles. The first SCLK cycle latches the most

significant bit on MOSI to select whether the desired operation is a read (R/W = 1) or a

write (R/W = 0). The following seven SCLK cycles are used to latch the slave register

read or write address.

NOTE

4-wire SPI interface mode is the default out of POR or after a

hard/soft reset. The 3-wire interface mode may be selected by

setting CTRL_REG0[SPIW] = 1.

3.2.2 SPI Write Operations with 3- and 4-Wire Modes

A write operation is initiated by transmitting a 0 for the R/W bit. Then, the 7-bit register

write address, A[6:0], is transmitted in MSb first order. The data byte to be written is

then transferred during the second 8 SCLK cycle period (again, with MSb first). Figure

8 and Figure 9 shows the bus protocol for a single byte register write operation in either

3- or 4-wire SPI modes.

SPI_CS_B

SCLK

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

MOSI

MISO

R/W A6 A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0

Figure 8. SPI single byte write protocol diagram (4-wire mode), R/W = 0

18

Freescale Semiconductor, Inc.

3-Axis Digital Angular Rate Gyroscope, Rev. 2.1, 5/2015