MT90222 Просмотр технического описания (PDF) - Zarlink Semiconductor Inc

Номер в каталоге

Компоненты Описание

производитель

MT90222 Datasheet PDF : 155 Pages

| |||

MT90222/3/4

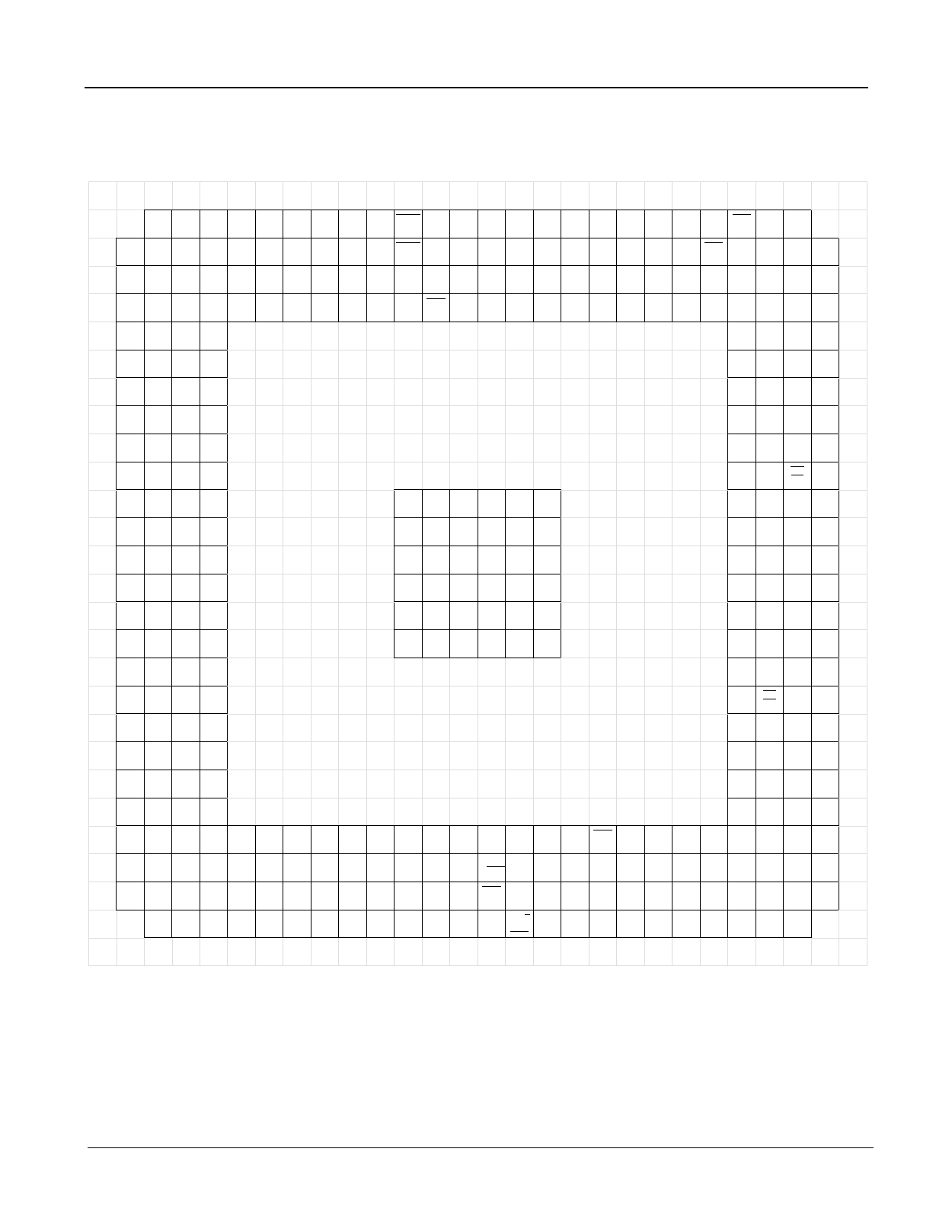

Pin Diagram - MT90224

The MT90224 uses a 384 pin PBGA with a 1.0 mm ball pitch.

Data Sheet

26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

A

DSTi[4] RXCKi VDD5 DSTi[2] RXSYN RXSYN TXRing- TXRing- TXRing- sr_cs_1 sr_a[1] sr_a[4] VDD5 sr_a[7] sr_a sr_a sr_a VDD5 sr_d[6] NC TMS Reset NC NC

A

[3]

Ci[1] Ci[0] Data[1] Data[5] Sync

[11] [15] [18]

B

NC VSS RXSYN DSTi[3] RXCKi DSTi[1] DSTi[0] TXRing- TXRing- TXRing- sr_cs_0 sr_a[0] sr_a[3] sr_a[5] sr_a[8] sr_a sr_a sr_d[0] sr_d[3] sr_d[7] TDI TRST Test4 NC VSS NC

B

Ci[4]

[2]

Data[0] Data[4] Data[7]

[12] [16]

C DSTi[5] NC

VSS RXCKi RXSYN RXSYN RXCKi Latch TXRing- TXRing- VDD5 NC sr_a[2] sr_a[6] sr_a

[4] Ci[3] Ci[2] [0]

Clk Data[2] Data[6]

[10]

sr_a sr_a sr_d sr_d[4] Test3 TDO VDD5 NC

[14] [17]

[1]

VSS URx URx

C

Data[0] Data[2]

D RXSYN RXSYN NC

Ci[6] Ci[5]

VSS V3.3 RXCKi VDD5 Test2 TXRing- V2.5 TXRing- sr_we V3.3 V2.5 sr_a[9] sr_a V3.3 sr_d[2] sr_d[5] TCK V3.3 VSS VSS URx URx URx

D

[1]

Data[3]

Clk

[13]

Data[1] Data[3] Data[4]

E DSTi[6] NC RXCKi V3.3

[5]

VSS URx VDD5 URx

E

Data[5]

Data[6]

F VDD5 DSTi[7] RXCKi RXSYN

[6] Ci[7]

V3.3 URx URx URx

F

Data[7] Data[8] Data[9]

G RXCKi DSTi[8] RXCKi RXSYN

[8]

[7] Ci[8]

URxD URxD URxD URxD G

ata[10] ata[11] ata[12] ata[13]

H VDD5 RXCKi RXSYN DSTi[9]

[9] Ci[9]

URxD URxD URx VDD5 H

ata[14] ata[15] Par

J RXSYN RXCKi RXSYN DSTi

Ci[11] [10] Ci[10] [10]

URx URx NC VDD5 J

SOC Clav

K RXSYN RXCKi DSTi V3.3

Ci[12] [11] [11]

V2.5 URx- URx URxA K

CLK Enb ddr[0]

L RXSYN RXCKi DSTi NC

Ci[13] [12] [12]

VSS VSS VSS VSS VSS VSS

URxA URxA URxA URxA L

ddr[2] ddr[1] ddr[3] ddr[4]

M DSTi RXSYN DSTi RXCKi

[14] Ci[14] [13] [13]

VSS VSS VSS VSS VSS VSS

UTx VDD5 UTx NC

M

Data[0]

Data[1]

N RXSYN VDD5 RXCKi V2.5

Ci[15]

[14]

VSS VSS VSS VSS VSS VSS

V3.3 UTx UTx UTx

N

Data[2] Data[3] Data[4]

P DSTi RXCKi DSTo V3.3

[15] [15] [15]

VSS VSS VSS VSS VSS VSS

V2.5 UTx VDD5 UTx

P

Data[6]

Data[5]

R TXCKio TXSyn NC DSTo

[15] cio[15]

[14]

VSS VSS VSS VSS VSS VSS

UTx UTxD UTxD UTxD R

Data[9] ata[10] ata[8] ata[7]

T TXCKio TXSyn TXCKio DSTo

[14] cio[14] [13] [13]

VSS VSS VSS VSS VSS VSS

UTxD VDD5 UTxD UTxD T

ata[13]

ata[12] ata[11]

U TXSyn DSTo TXCKio V2.5

cio[13] [12] [12]

V3.3 UTxPar UTxD UTxD U

ata[15] ata[14]

V VDD5 TXSyn DSTo TXCKio

cio[12] [11] [11]

UTxClk UTx UTx UTx

V

Enb Clav SOC

W TXSyn DSTo TXCKio TXSyn

cio[11] [10] [10] cio[10]

UTx UTx UTx UTx W

Addr[2] Addr[3] Addr[1] Addr[0]

Y DSTo TXCKio TXSyn DSTo

[9]

[9] cio[9] [8]

UTx REFCK VDD5 NC

Y

Addr[4] [0]

AA TXCKio VDD5 TXSyn V3.3

[8]

cio[8]

REFCK REFCK NC REFCK AA

[2]

[3]

[1]

AB DSTo TXCKio TXSyn VSS

[7]

[7] cio[7]

V3.3 VDD5 PLL PLL AB

REF[1] REF[0]

AC DSTo TXCKio DSTo VSS V3.3 TXSyn NC VDD5 DSTo V3.3 RXRing RXRing V2.5 V3.3 up_a up_a[7] V2.5 up_irq NC up_d V3.3 VSS VSS NC

NC

Clk

AC

[6]

[6]

[5]

cio[5]

[1]

Data[7] Data[4]

[10]

[10]

AD TXSyn VDD5 VSS NC

NC

NC TXSyn TXSyn TXSyn DSTo TXSyn VDD5 RXRing up_oe VDD5 up_a[6] up_a[3] up_a[0] up_d up_d up_d[8] up_d[5] up_d[2] VSS NC Test1 AD

cio[6]

cio[4] cio[3] cio[2] [0] cio[0]

Data[1] or up_rd

[14] [11]

AE

NC VSS NC

NC TXCKio DSTo DSTo DSTo TXCKio NC RXRing RXRing RXRing up_cs up_a up_a[8] up_a[4] up_a[1] up_d up_d VDD5 up_d[6] up_d[4] up_d[1] VSS NC

AE

[5]

[4]

[3]

[2]

[1]

Data[6] Data[3] Data[0]

[11]

[15] [12]

AF

NC NC NC NC TXCKio TXCKio TXCKio TXSyn TXCKio RXRing RXRing RXRing RXRing up_r/w up_a[9] up_a[5] up_a[2] VDD5 up_d up_d[9] up_d[7] NC up_d[3] up_d[0]

AF

[4]

[3]

[2] cio[1] [0] Data[5] Data[2] Sync Clk

or

[13]

up_wr

26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

Figure 4 - MT90224 Pinout (Bottom View)

13

Zarlink Semiconductor Inc.