82545GM Просмотр технического описания (PDF) - Intel

Номер в каталоге

Компоненты Описание

производитель

82545GM Datasheet PDF : 55 Pages

| |||

82545GM — Networking Silicon

3.2.4

3.2.5

3.2.6

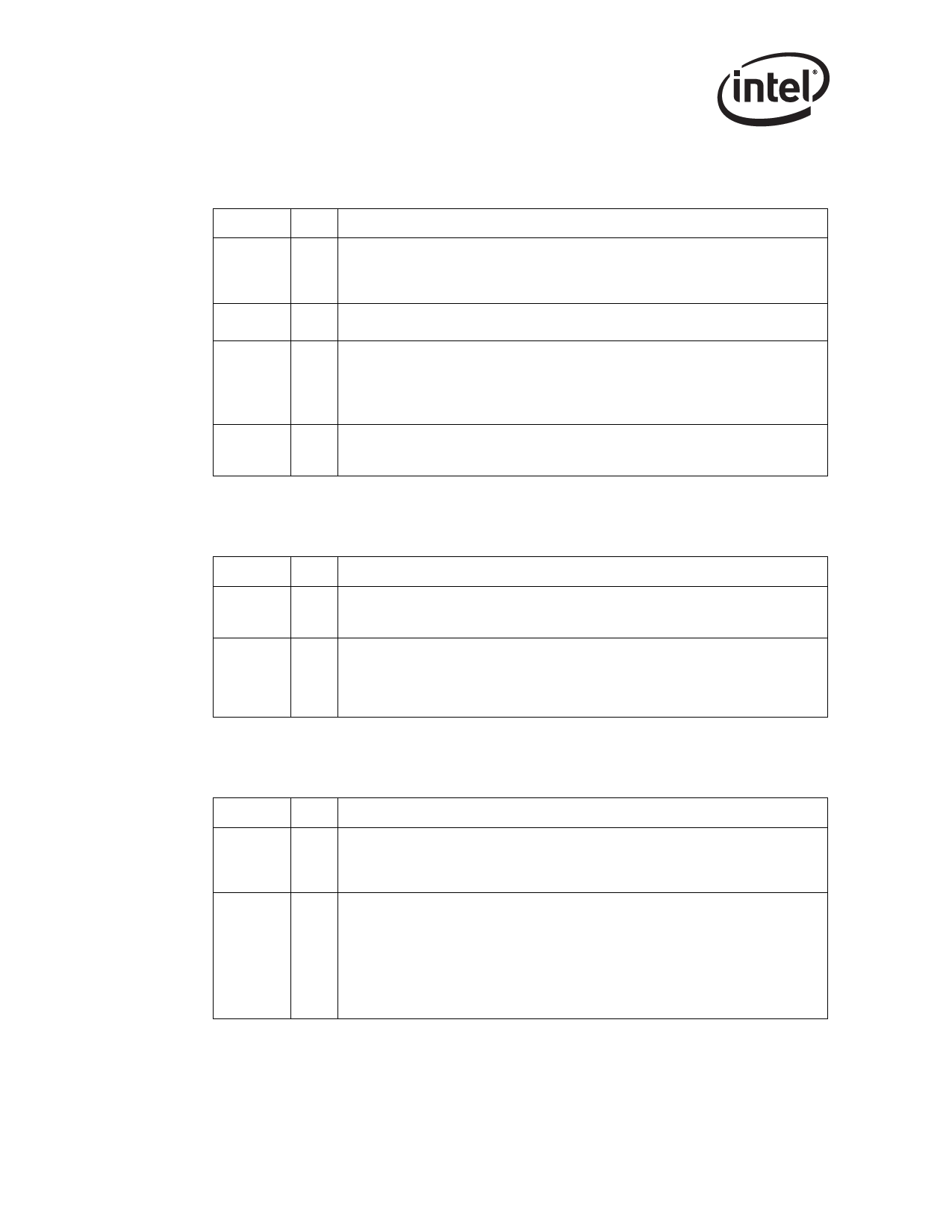

System Signals

Symbol

CLK

M66EN

RST#

LAN_

PWR_

GOOD

Type

Name and Function

PCI Clock. The PCI Clock signal provides timing for all transactions on the PCI bus and

I

is an input to the 82545GM device. All other PCI signals, except the Interrupt A

(INTA#) and PCI Reset signal (RST#), are sampled on the rising edge of CLK. All other

timing parameters are defined with respect to this edge.

I

66 MHz Enable. The 66 MHz Enable signal is used to indicate whether or not the

system bus is capable of supporting an operating frequency of 66 MHz.

PCI Reset. When the PCI Reset signal is asserted, all PCI output signals, except the

Power Management Event signal (PME#), are floated and all input signals are ignored.

I

The PME# context is preserved, depending on power management settings.

Most of the internal state of the 82545GM is reset on the de-assertion (rising edge) of

RST#.

Power Good (Power-on Reset). The Power Good signal is used to indicate that stable

I

power is available for the 82545GM. When the signal is low, the 82545GM holds itself

in reset state and floats all PCI signals.

Error Reporting Signals

Symbol

SERR#

PERR#

Type

Name and Function

System Error. The System Error signal is used by the 82545GM controller to report

OD address parity errors. SERR# is open drain and is actively driven for a single PCI clock

when reporting the error.

Parity Error. The Parity Error signal is used by the 82545GM controller to report data

parity errors during all PCI transactions except by a Special Cycle. PERR# is sustained

STS tri-state and must be driven active by the 82545GM controller two data clocks after a

data parity error is detected. The minimum duration of PERR# is one clock for each

data phase a data parity error is present.

Power Management Signals

Symbol Type

Name and Function

PME#

OD

AUX_PWR I

Power Management Event. The 82545GM device drives this signal low when it

receives a wake-up event and either the PME Enable bit in the Power Management

Control/Status Register or the Advanced Power Management Enable (APME) bit of the

Wake-up Control Register (WUC) is 1b.

Auxiliary Power. If the Auxiliary Power signal is high, then auxiliary power is available

and the 82545GM device should support the D3cold power state.

Note that AUX_PWR is not a supply input, but is an indication of whether AUX_PWR is

available to the 82545GM and/or subsystem. Setting AUX_PWR to 1b enables

advertising D3cold Wake Up support and changes the reset function of PME_En and

PME_Status. AUX_PWR is level sensitive, and any changes are immediately reflected

in the D3cold Wake Up advertisements and the PME_En and PME_Status behavior on

PCI reset.

12

Datasheet