ADP3020 Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

ADP3020 Datasheet PDF : 22 Pages

| |||

ADP3020

Synchronous Rectifier (DRVL)

Synchronous rectification is used to reduce conduction losses

and to ensure proper start-up of the boost gate driver circuit.

Antishoot-through protection has been included to prevent cross

conduction during switch transitions. The low side driver must

be turned off before the high side driver is turned on. For typi-

cal N-channel MOSFETs, the dead time is about 50 ns. On the

other edge, a dead time of about 50 ns is achieved by an internal

delay circuit. The synchronous rectifier is turned off when the

current flowing through the low-side MOSFET falls to zero when

in Discontinuous Conduction (DCM) PWM mode and PSV mode.

In Continuous Conduction (CCM) PWM mode, the current

flowing through the low-side MOSFET never reaches zero, so the

synchronous rectifier is turned off by the next clock cycle.

Oscillator Frequency and Synchronization (SYNC)

The SYNC pin controls the oscillator frequency. When SYNC

= 0 V, fOSC = 200 kHz ; when SYNC = REF, fOSC = 300 kHz;

when SYNC = 5 V, fOSC = 400 kHz. 400 kHz operation will

minimize external component size and cost while 200 kHz opera-

tion provides better efficiency and lower dropout. The SYNC

pin can also be used to synchronize the oscillator with an exter-

nal 5 V clock signal. A low-to-high transition on SYNC initiates

a new cycle. Synchronization range is 230 kHz to 600 kHz.

Shutdown (SD)

Holding SD = GND low will put the ADP3020 into ultralow

current shutdown mode. For automatic start-up, SD can be tied

directly to VIN.

Soft-Start and Power-Up Sequencing (SS)

SS3 and SS5 are soft start pins for the two controllers. A 4 µA

pull-up current is used to charge an external soft start capacitor.

Power-up sequencing can be easily done by choosing different

size external capacitors. When SS3/SS5 < 1.2 V, the two switch-

ing regulators are turned off. When 1.2 V < SS5/SS3 < 2.6 V,

the regulators start working in soft start mode. When SS3/SS5 >

2.6 V, the regulators are in normal operating mode. The con-

trollers are forced to stay in PWM mode during the soft-start

period. The minimum soft-start time (~20 µs) is set by an inter-

nal capacitor. Table II shows the ADP3020 operating modes.

Current Limiting (CLSET)

A cycle-by-cycle current limiting scheme is used by monitoring

current through the top N-channel MOSFET when it is turned

on. By measuring the voltage drop across the high-side MOSFET

VDS(ON), the external sense resistor can be deleted. The current

limit value can be set by CLSET. When CLSET = Floating, the

maximum VDS(ON) = 72 mV at room temperature; when CLSET

= 0 V, the maximum VDS(ON) = 144 mV at room temperature. An

external resistor can be connected between CLSET and AGND

to choose a value between 72 mV and 144 mV. The temperature

coefficient of RDS(ON) of the N-channel MOSFET is canceled by

the internal current limit circuitry, so that an accurate current

limit value can be obtained over a wide temperature range. In

PSV mode, the current limit value is reduced to about 1/4 of

the value in PWM mode to reduce the interference noise to other

components on the PC board.

Output Undervoltage Protection

Each switching controller has an undervoltage protection circuit.

When the current flowing through the high-side MOSFET

reaches the current limit continuously for eight clock cycles,

and the output voltage is below 20% of the nominal output

voltage, both controllers will be latched off and will not restart

until SD or SS3/SS5 is toggled, or until VIN is cycled below 4 V.

This feature is disabled during soft start.

Output Overvoltage Protection

Both converter outputs are continuously monitored for overvolt-

age. If either output voltage is higher than the nominal output

voltage by more than 20%, both converter’s high-side gate drivers

(DRVH5/3) will be latched off, and the low-side gate drivers

will be latched on, and will not restart until SD or SS5/SS3 are

toggled, or until VIN is cycled below 4 V. The low-side gate

driver (DRVL) is kept high when the controller is in off-state

and the output voltage is less than 93% of the nominal output

voltage. Discharging the output capacitors through the main

inductor and low-side N-channel MOSFET will cause the out-

put to ring. This will make the output momentarily go below

GND. To prevent damage to the circuit, use a reverse-biased

1 A Schottky diode across the output capacitors to clamp the

negative surge.

Power Good Output (PWRGD)

The ADP3020 also provides a PWRGD signal for the micropro-

cessor. During start-up, the PWRGD pin is held low until 5 V

output is within –4% of its preset voltage. Then, after a time

delay determined by an external timing capacitor connected from

CPOR to GND, PWRGD will be actively pulled up to INTVCC

by an external pull-up resistor. CPOR can also be used as a

manual reset (MR) function. When the 5 V output is lower than

the preset voltage by more than 8%, PWRGD is immediately

pulled low.

Linear Regulator Controller

The ADP3020 includes an onboard linear regulator controller.

An external PNP transistor can be used for operation up to 1 A.

For higher output current applications, a low threshold PMOS

can be used as the pass transistor. The output voltage can be set

by a resistor divider. The minimum output voltage of the LDO

is 1.25 V, while the maximum output voltage depends on where

the LDO input is connected and the dropout voltage of the

external pass transistor.

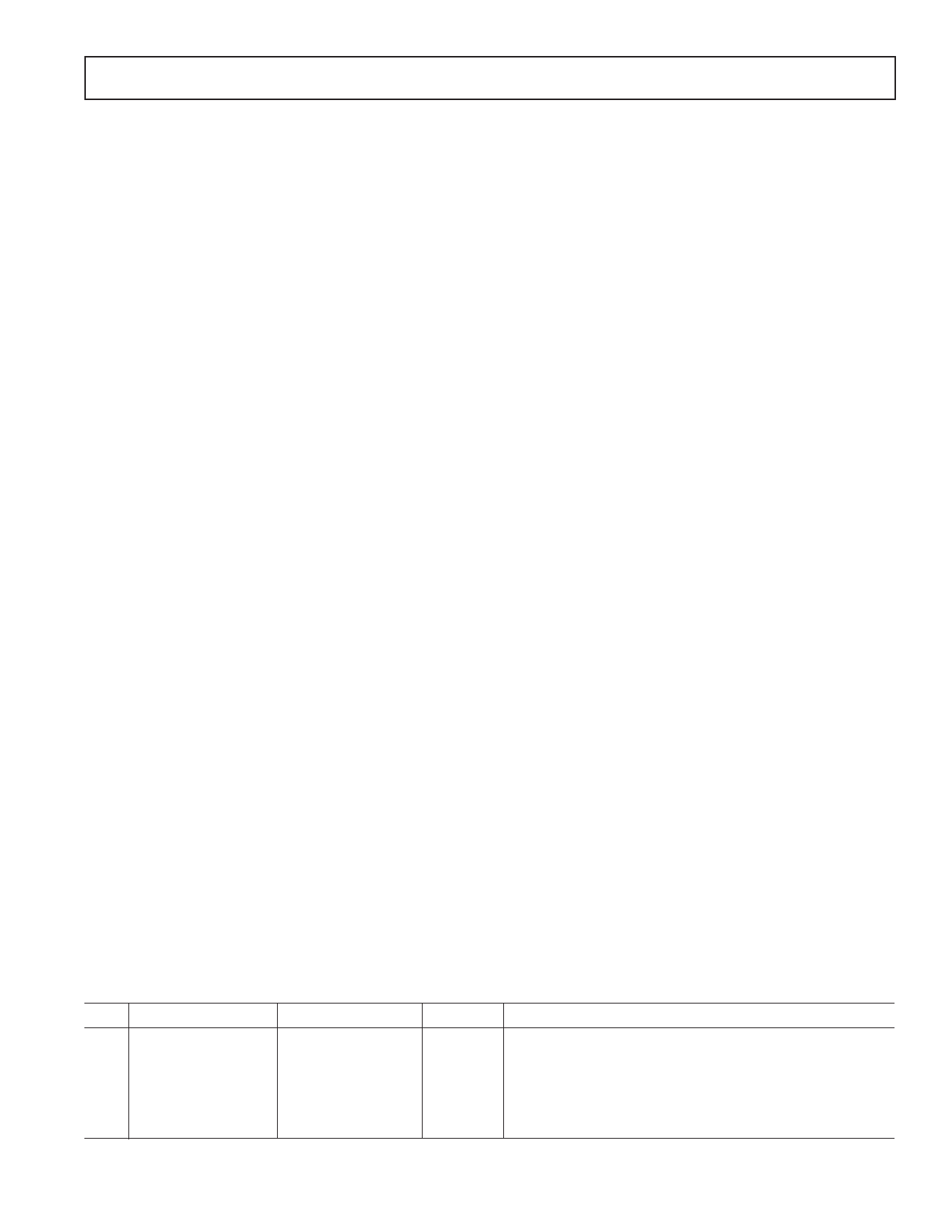

SD

Low

High

High

High

High

High

Table II. Operating Modes

SS5

X

SS5 < 1.2 V

1.2 V < SS5 < 2.6 V

2.6 V < SS5

X

X

SS3

X

SS3 < 1.2 V

X

X

1.2 V < SS3 < 2.6 V

2.6 V < SS3

Mode

Shutdown

Standby

Run

Run

Run

Run

Description

All Circuits Turned Off

5 V and 3.3 V Off; INTVCC = 5 V, REF = 1.2 V

5 V in Soft Start

5 V in Normal Operation

3.3 V in Soft Start

3.3 V in Normal Operation

REV. 0

–11–