LC6512A(2001) Просмотр технического описания (PDF) - SANYO -> Panasonic

Номер в каталоге

Компоненты Описание

производитель

LC6512A

(Rev.:2001)

(Rev.:2001)

LC6512A Datasheet PDF : 24 Pages

| |||

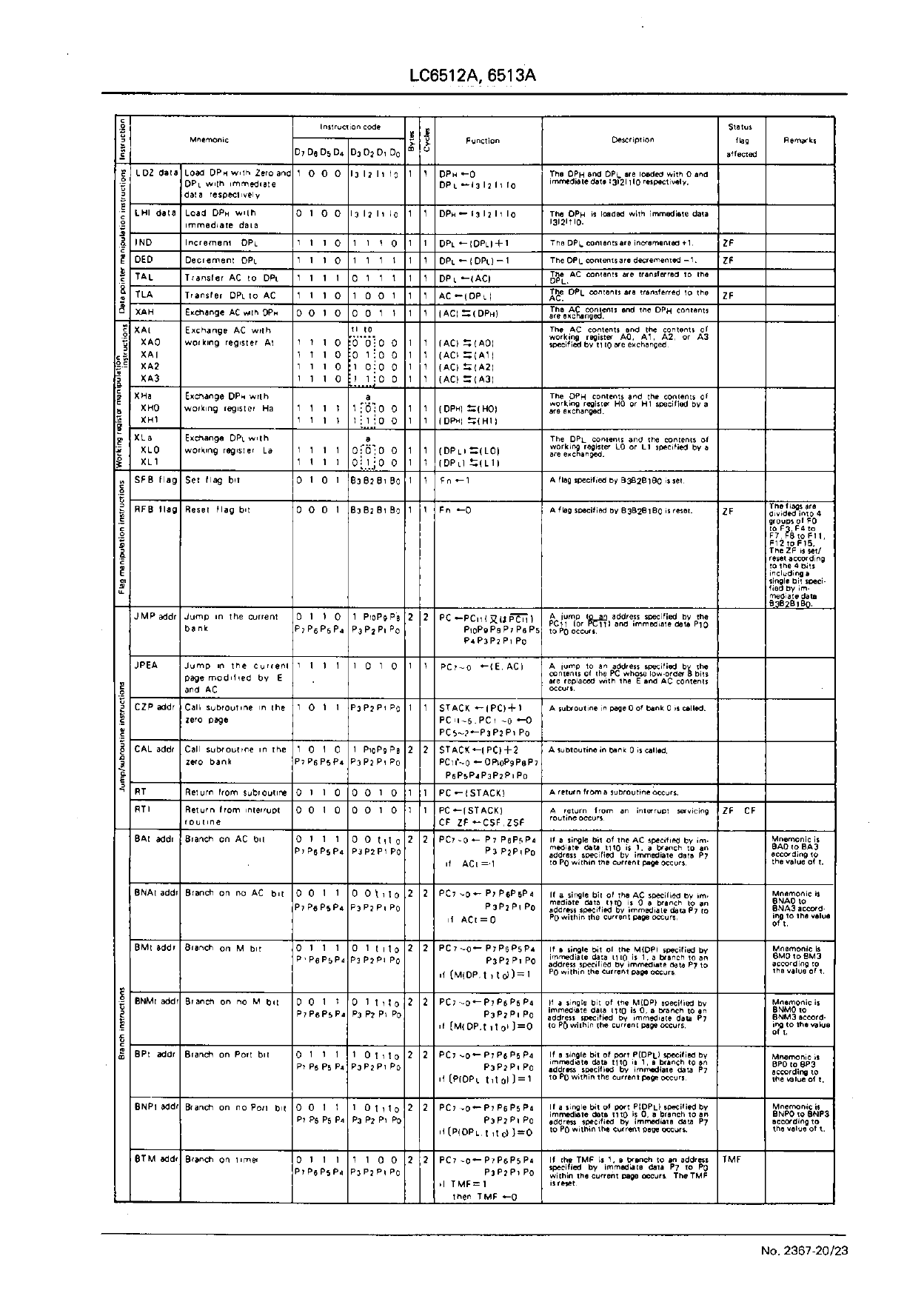

LC6512A, LC6513A

Mnemonic

Instruction code

D7D6D5D4 D3D2D1D0

LDZ

date

Load DPH With Zero and

DPL with immediate data

respectively

LHI data Load DPH with

immediate data

lND

Increment DPL

1000

0100

1110

I3 I2 I1 I0 1

I3 I2 I1 I0 1

1110 1

DED Decrement DPL

1110 1111 1

TAL

Transfer AC to DPL 1 1 1 1 0 1 1 1 1

TLA

Transfer DPL to AC 1 1 1 0 1 0 0 1 1

XAH

Exchange AC with

DPH

XAt

XA0

XA1

XA2

XA3

Exchange AC with

working register At

XHa

XH0

XH1

XLa

XL0

XL1

Exchange DPH with

working register Ha

Exchange DPL with

working register La

SFB flag Set flag bit

0010 0011 1

1110

1110

1110

1110

1111

1111

1111

1111

0101

t1 t0

0000 1

0100 1

1000 1

1100 1

a

1000 1

1100 1

a

0000 1

0100 1

B3B2B1B0 1

RFB

flag

Reset flag bit

0 0 0 1 B3B2B1B0 1

JMP

addr

JPEA

CZP

addr

CAL

addr

RT

RTI

BAt

addr

Jump in the current

bank

0 1 1 0 1 P10P9P8 2

P7P6P5P4 P3P2P1P0

Jump in the current

page modified by E

and AC

1111 1010 1

Call subroutine in the 1 0 1 1 P3P2P1P0 1

Zero Page

Call subroutine in the 1 0 1 0 1 P10P9P8 2

zero bank

P7P6P5P4 P3P2P1P0

Return from

subroutine

Returnn from interrupt

routine

0110

0010

0010 1

0010 1

Branch on AC bit

0 1 1 1 0 0 t1 t0 2

P7P6P5P4 P3P2P1P0

BNAt

addr

Branch on no AC bit 0 0 1 1 0 0 t1 t0 2

P7P6P5P4 P3P2P1P0

BMt

addr

Branch on M bit

0 1 1 1 0 1 t1 t0 2

P7P6P5P4 P3P2P1P0

BNMt

addr

Branch on no M bit

0 0 1 1 0 1 t1 t0 2

P7P6P5P4 P3P2P1P0

BPt

addr

Branch on Port bit

0 1 1 1 1 0 t1 t0 2

P7P6P5P4 P3P2P1P0

BNPt

addr

Branch on no Port bit 0 0 1 1 1 0 t1 t0 2

P7P6P5P4 P3P2P1P0

BTTM Branch on timer

addr

0111 1100 2

P7P6P5P4 P3P2P1P0

Function

Description

Status

flag

affected

Remarks

1 DPH←0

DPL←I3I2I1I0

The DPH and DPL are loaded with 0 and

immediate data I3I2I1I0 respectively.

1 DPH←I3I2I1I0

1 DPL←(DPL)+1

1 DPL←(DPL)–1

1 DPL←(AC)

1 AC←(DPL)

1 (AC)← (DPH)

The DPH is loaded with immediate

data I3I2I1I0.

The DPL contents are incremented ZF

+1.

The DPL contents are decremented

–1.

ZF

The AC contents are transferred to

the DPL.

The DPL contents are transferred to

the AC.

ZF

The AC contents and the DPH

contents are exchanged.

1 (AC)← (A0)

1 (AC)← (A1)

1 (AC)← (A2)

1 (AC)← (A3)

1

1

((DDPPHH))←←

(H0)

(H1)

1

1

((DDPPLL))←←((LL01))

1 Fn←1

1 Fn←0

The AC contents and the contents of

working register A0, A1, A2, or A3

specified by t1 t0 are exchanged.

The DPH contents and the contents

of working register H0 or H1 specified

by a are exchanged.

The DPL contents and the contents of

working register L0 or L1 specified by

a are exchanged.

A flag specified by B3B2B1B0 is set.

A flag specified by B3B2B1B0 is

ZF

reset.

2 PC←PC11(orPC11) A jump to an address specified by the

P10P9P8P7P6P5 PC11(or PC11)and immediate data

P4P3P2P1P0

P10 to P0 occurs.

1 PC7 to 0 ←(E, AC)

A jump to an address specified by the

contents of the PC whose low-order 8

bits are replaced with the E and AC

contents occurs.

1 STACK←(PC)+1

A subroutine in page 0 of bank 0 is

PC11 to 6.PC1 to 0←0

PC5 to 2←P3P2P1P0

called.

2 STACK←(PC)+2

A subroutine in bank 0 is called.

PC11* to 0←OP10P9

P8P7P6P5P4P3P2P1P0

1 PC←(STACK)

A return from a subroutine occurs.

The flags are

divided into 4

groups of F0 to

F3,F4 to F7,F8 to

F11,F12 to F15.

The ZF is set/reset

according to the 4

bits including a

single bit specified

bit specified by

immediate data

B3B2B1B0.

1 PC←(STACK)

A return from an lnterrupt servicing

CF ZF←CSF.ZSF routine occurs.

ZF CF

2

PC7 to 0←P7P6P5P4

P3P2P1P0

If a single bit of the AC specified by

immediate data t1 t0 is 1,a branch to an

address specified by immediate data P7

If ACt=1

to P0 within the current page occurs.

2 PC7 to 0←P7P6P5P4 If a single bit of the AC specified by

P3P2P1P0

immediate data t1t0 is 0,a branch to an

address specified by immediate data P7

If ACt=0

to P0 within the current page occurs.

2 PC7 to 0←P7P6P5P4 If a single bit of the M(DP) specified by

P3P2P1P0

immediate data t1t0 is 1,a branch to an

address specified by immediate data P7

If [M(DP.t1t0)]=1

to P0 within the current page occurs.

2

PC7 to 0←P7P6P5P4

P3P2P1P0

If a single bit of the M(DP) specified by

immediate data t1t0 is 0,a branch to an

address specified by immediate data P7

If [M(DP.t1t0)]=0

to P0 within the current page occurs.

2 PC7 to 0←P7P6P5P4 If a single bit of port P(DPL) specified by

P3P2P1P0

immediate data t1 t0 is 1,a branch to an

address specified by immediate data P7

If [P(DPL.t1t0)]=1

toP0 within the current page occurs.

2 PC7 to 0←P7P6P5P4 If a single bit of port P(DPL) specified by

P3P2P1P0

immediate data t1 t0 is 0,a branch to an

address specified by immediate data P7

If [P(DPL.t1t0)]=0

to P0 within the current page occurs.

Mnemonic is

BA0 to BA3

according to

the value of t.

Mnemonic is

BNA0 to BNA3

according to

the value of t.

Mnemonic is

BM0 to BM3

according to

the value of t.

Mnemonic is

BNM0 to

BNM3

according to

the value of t.

Mnemonic is

BP0 to BP3

according to

the value of t.

Mnemonic is

BNP0 to BNP3

according to

the value of t.

2 PC7 to 0←P7P6P5P4 If theTMF is 1,a branch to an address

P3P2P1P0 specified by immediate data P7 to P0

If TMF=1

within the current page occurs.The TMF

then TMF←0

is reset.

TMF

No.2367–20/24