IDT82P2281 Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

производитель

IDT82P2281 Datasheet PDF : 375 Pages

| |||

IDT82P2281

SINGLE T1/E1/J1 LONG HAUL / SHORT HAUL TRANSCEIVER

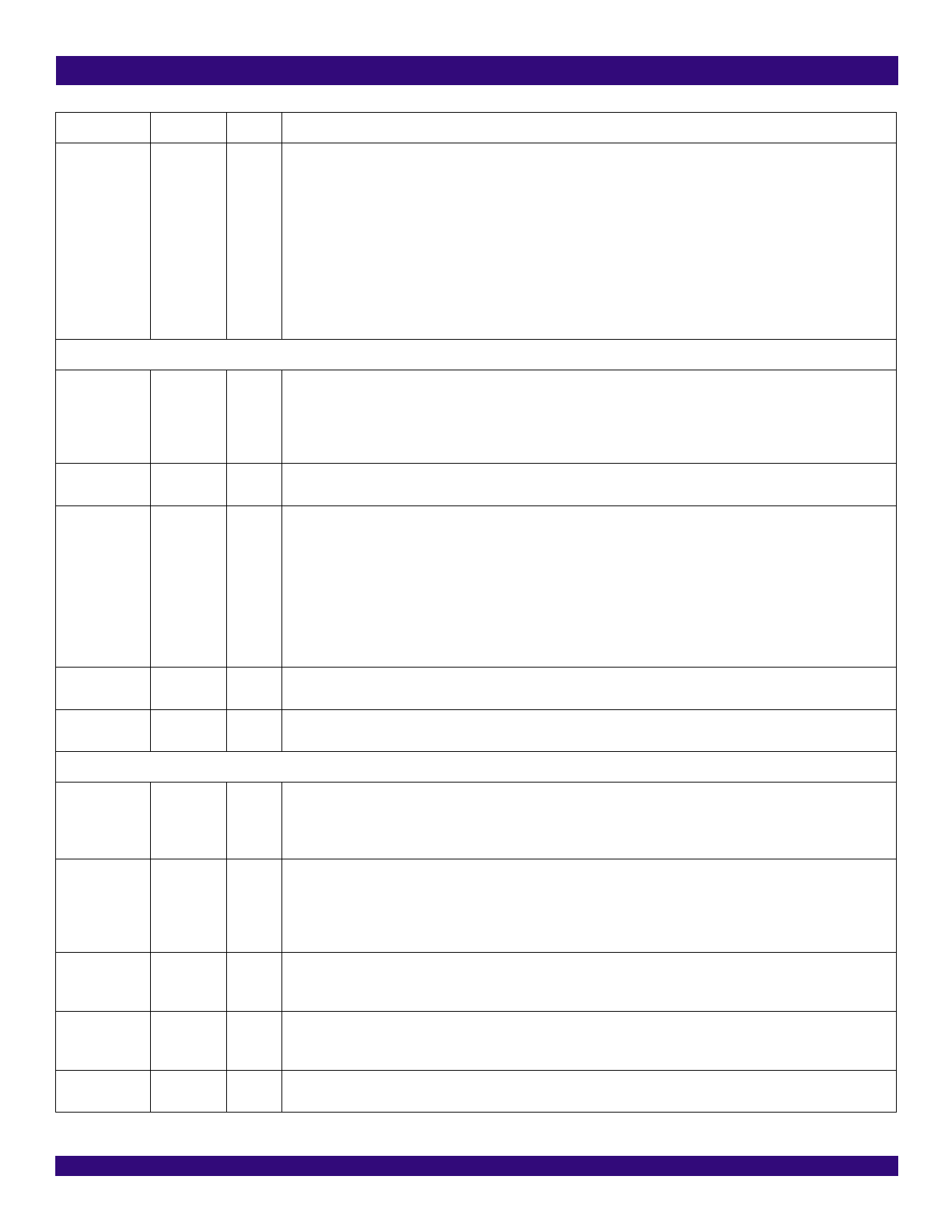

Name

Type Pin No.

Description

TSCK / MTSCK Output / Input 56 TSCK: Transmit Side System Clock

In Transmit Clock Master mode, TSCK outputs a (gapped) 1.544 MHz (for T1/J1 mode) / 2.048 MHz (for E1 mode) clock

used to sample the signal on the TSD and TSIG pins and update the signal on the TSFS pin.

In Transmit Clock Slave mode, TSCK inputs a 1.544 MHz (for T1/J1 mode only), 2.048 MHz or 4.096 MHz clock used to

sample the signal on the TSD, TSIG and TSFS pins.

MTSCK: Multiplexed Transmit Side System Clock

In Transmit Multiplexed mode, MTSCK inputs a 8.192 MHz or 16.384 MHz clock used to sample the signal on the MTSD,

MTSIG and MTSFS pins.

TSCK/MTSCK is a Schmitt-triggered input/output with pull-up resistor.

Clock Generator

OSCI

Input

OSCO

CLK_SEL[0]

CLK_SEL[1]

CLK_SEL[2]

Output

Input

CLK_GEN

REFA_OUT

Output

Output

75 OSCI: Crystal Oscillator Input

This pin is connected to an external clock source.

The clock frequency of OSCI is defined by CLK_SEL[2:0]. The clock accuracy should be ±32 ppm and duty cycle should

be from 40% to 60%.

Hardware or software reset can only be applied when the clock on this pin is available.

74 OSCO: Crystal Oscillator Output

This pin outputs the inverted, buffered clock input from OSCI.

65 CLK_SEL[2:0]: Clock Selection

66 These three pins select the input clock signal:

67 When the CLK_SEL[2] pin is low, the input clock signal is N X 1.544 MHz;

when the CLK_SEL[2] pin is high, the input clock signal is N X 2.048 MHz.

When the CLK_SEL[1:0] pins are ‘00’, the N is 1;

when the CLK_SEL[1:0] pins are ‘01’, the N is 2;

when the CLK_SEL[1:0] pins are ‘10’, the N is 3;

when the CLK_SEL[1:0] pins are ‘11’, the N is 4.

CLK_SEL[2:0] are Schmitt-trigger inputs.

61 CLK_GEN: Clock Generator

This pin outputs the 1.544/2.048 MHz clock signal generated by the Clock Generator.

70 REFA_OUT: Reference Clock Output A

This pin outputs a recovered clock from the Clock and Data Recovery function block.

RESET

GPIO

THZ

INT

REFR

Control Interface

Input

64 RESET: Reset (Active Low)

A low pulse for more than 100 ns on this pin resets the device. All the registers are accessible 2 ms after the reset.

Reset can only be applied when the clock on the OSCI pin is available.

The RESET pin is a Schmitt-trigger input with a weak pull-up resistor.

Output / Input 1 General Purpose I/O

This pin can be defined as input pin or output pin by the DIR0 bit (b0, T1/J1-006H / b0, E1-006H). When the pin is input,

its polarity is indicated by the LEVEL0 bit (b2, T1/J1-006H / b2, E1-006H). When the pin is output, its polarity is controlled

by the LEVEL0 bit (b2, T1/J1-006H / b2, E1-006H).

GPIO is a Schmitt-trigger input/output with a pull-up resistor

Input

Output

2 THZ: Transmit High-Z

A high level on this pin puts the TTIP/TRING pins into high impedance state.

THZ is a Schmitt-trigger input.

39 INT: Interrupt (Active Low)

This is the open drain, active low interrupt output. This pin will stay low until all the active unmasked interrupt indication

bits are cleared.

Output

9 REFR:

This pin should be connected to ground via an external 10K resistor.

Pin Description

6

October 7, 2003