IDT82P2281 Просмотр технического описания (PDF) - Integrated Device Technology

Номер в каталоге

Компоненты Описание

производитель

IDT82P2281 Datasheet PDF : 375 Pages

| |||

IDT82P2281

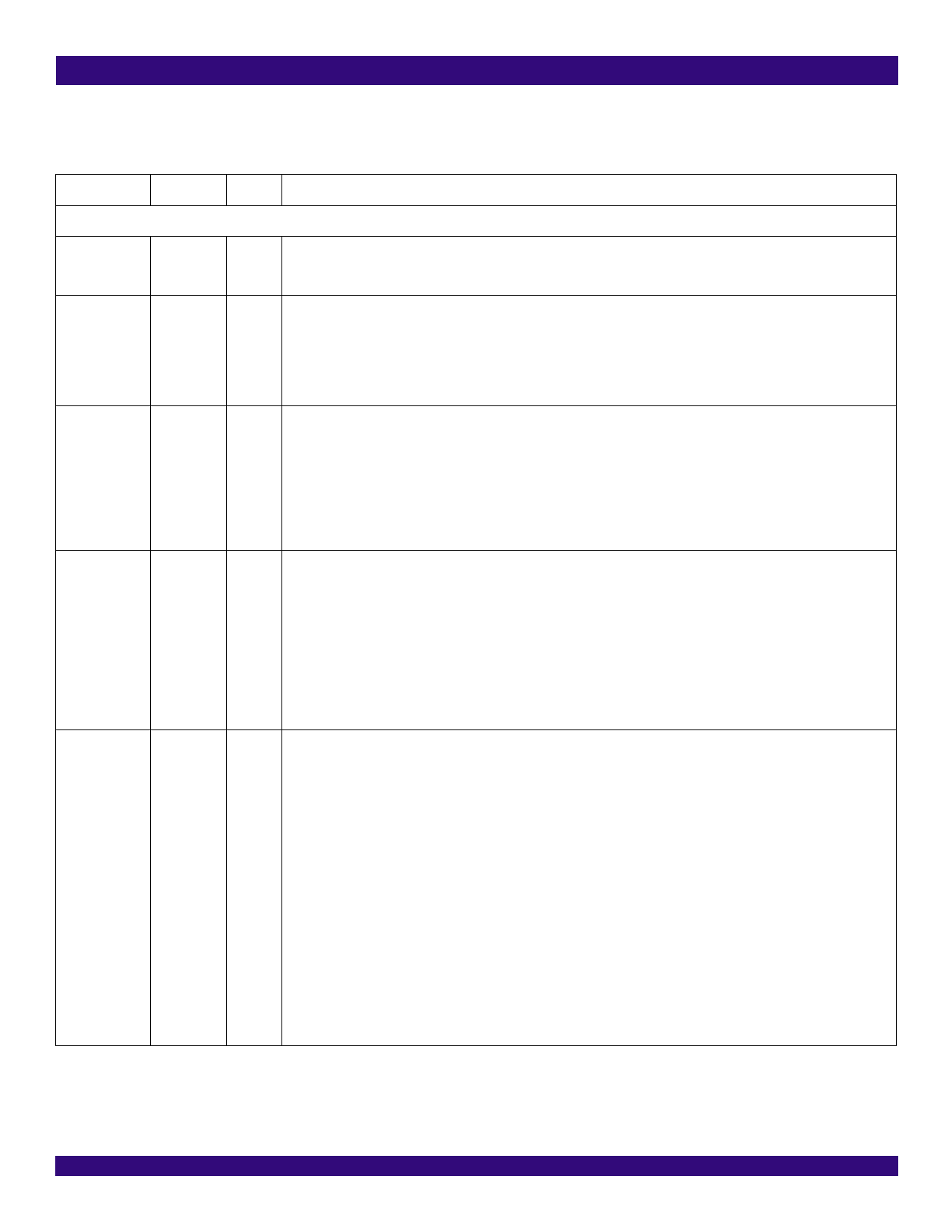

2 PIN DESCRIPTION

SINGLE T1/E1/J1 LONG HAUL / SHORT HAUL TRANSCEIVER

Name

RTIP

RRING

TTIP

TRING

RSD / MRSD

Type

Input

Output

Output

Pin No.

Description

Line and System Interface

17 RTIP / RRING: Receive Bipolar Tip/Ring

These pins are the differential line receiver inputs.

18

11 TTIP / TRING: Transmit Bipolar Tip/Ring

These pins are the differential line driver outputs and can be set to high impedance state. A logic high on the THZ pin

12 sets both two pins to high impedance state. When the T_HZ bit (b4, T1/J1-023H / b4, E1-023H) is set to ‘1’, these two

pins will also be set to high impedance state.

Besides, TTIP/TRING will also be set to high impedance state by other ways (refer to Chapter 3.25 Line Driver for

details).

59 RSD: Receive Side System Data

The processed data stream is output on this pin.

In Receive Non-Multiplexed mode, the RSD pin is updated on the active edge of RSCK.

RSIG / MRSIG Output

MRSD: Multiplexed Receive Side System Data

In Receive Multiplexed mode, the MRSD pin is used to output the processed data stream. Using a byte-interleaved mul-

tiplexing scheme, the MRSD pin outputs the data from the link. The data on the MRSD pin is updated on the active edge

of MRSCK.

58 RSIG: Receive Side System Signaling

The extracted signaling bits are output on this pin. They are located in the lower nibble (b5 ~ b8) and are channel/

timeslot-aligned with the data output on the RSD pin.

In Receive Non-Multiplexed mode, the RSIG pin is updated on the active edge of RSCK.

MRSIG: Multiplexed Receive Side System Signaling

In Receive Multiplexed mode, the MRSIG pin is used to output the extracted signaling bits. The signaling bits are located

in the lower nibble (b5 ~ b8) and are channel/timeslot-aligned with the data output on the MRSD pin. Using the byte-inter-

leaved multiplexing scheme, the MRSIG pin outputs the signaling bits from the link. The signaling bits on the MRSIG pin

is updated on the active edge of the MRSCK.

RSFS / MRSFS Output / Input 57 RSFS: Receive Side System Frame Pulse

In T1/J1 Receive Clock Master mode, RSFS outputs the pulse to indicate each F-bit, every second F-bit in SF frame, the

first F-bit of every SF/ESF/T1 DM/SLC-96 multi-frame or the first F-bit of every second SF multi-frame.

In T1/J1 Receive Clock Slave mode, RSFS inputs the pulse at a rate of integer multiple of 125 µs to indicate the start of

a frame.

In E1 Receive Clock Master mode, RSFS outputs the pulse to indicate the Basic frame, CRC Multi-frame, Signaling

Multi-frame, or both the CRC Multi-frame and Signaling Multi-frame, or the TS1 and TS16 overhead.

In E1 Receive Clock Slave mode, RSFS inputs the pulse at a rate of integer multiple of 125 µs to indicate the start of a

frame.

RSFS is updated/sampled on the active edge of RSCK. The active polarity of the RSFS is selected by the FSINV bit (b4,

T1/J1-048H / b4, E1-048H).

MRSFS: Multiplexed Receive Side System Frame Pulse

In Receive Multiplexed mode, MRSFS inputs the pulse at a rate of integer multiple of 125 µs to indicate the start of a

frame on the multiplexed data bus. MRSFS is sampled on the active edge of MRSCK. The active polarity of MRSFS is

selected by the FSINV bit (b4, T1/J1-048H / b4, E1-048H).

RSFS/MRSCK is a Schmitt-triggered input/output with pull-up resistor.

Pin Description

4

October 7, 2003