HMS30C7202N Просмотр технического описания (PDF) - MagnaChip Semiconductor

Номер в каталоге

Компоненты Описание

производитель

HMS30C7202N Datasheet PDF : 179 Pages

| |||

HMS30C7202N

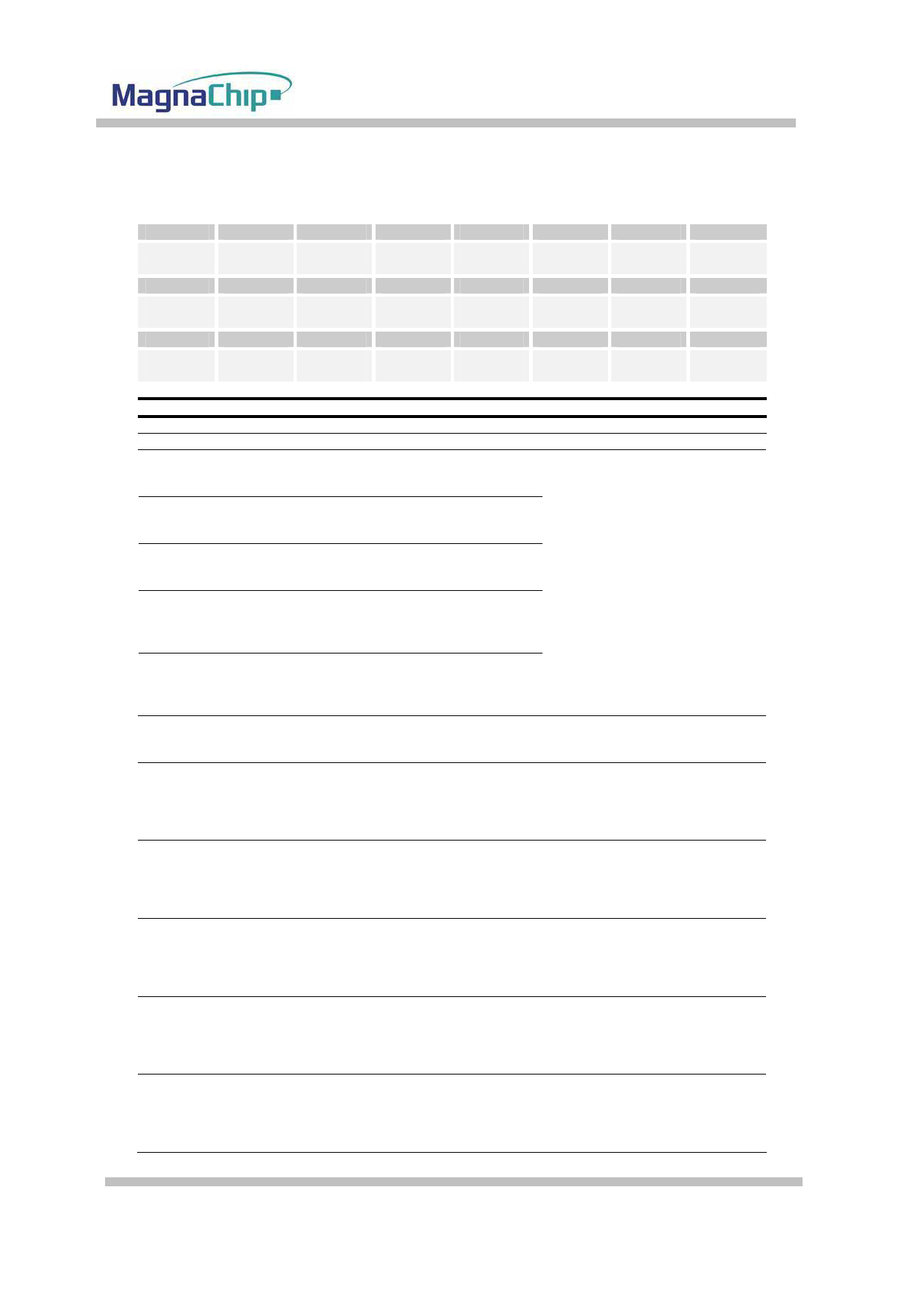

read each time the ARM exits reset mode, so that the ARM can identify what event has caused it to exit from

reset mode.

0x80001020

16

WARM

RESET

15

14

13

12

11

10

9

8

HOTSYNC

INTR

ADAPTOR

INTR

RTC INTR

MRING

INTR

WAKEUP

INTR

HOTSYNC

STATUS

WDT RST

WARM RST

STATUS

7

6

5

4

3

2

1

0

ADAPTOR RTC

STATUS STATUS

MRING

STATUS

WAKEUP

STATUS

PLL3

LOCK

PLL2

LOCK

PLL1

LOCK

POR

STATUS

Bits

31:17

16

15

Type

-

W

R/W

14 R/W

13 R/W

12 R/W

11 R/W

10 R/w

9

R/w

8

R/w

7

R/w

6

R/w

5

R/w

Function

Reserved

Warm RESET. Writing a `1' causes nRESET to be asserted. Writing `0' has no effect.

HOTSYNC interrupt Mask. When reads,

When writes to these bits, PMU

0 = Disable Hotsync interrupt from External pin.

Interrupts will be enabling. `1' enables

1 = Enable Hotsync interrupt from External pin.

interrupts to the CPU, `0' masks such

No External Power Interrupt Mask. When reads,

activity. Should the enable bit be set

0 = Disable PMU interrupt from PMADAPOK LOW. to one when one of the debounced

1 = Enable PMU interrupt from PMADAPOK LOW. event signals is set, then an interrupt

RTCEvt Interrupt Mask. When reads,

WILL be generated (i.e. the interrupt

0 = Disable PMU interrupt from RTC

is level sensitive, not edge sensitive).

1 = Enable PMU interrupt from RTC

RIEvt Interrupt MASK PMU Interrupt Request / Clear

When reads,

0 = Disable PMU interrupt from MRING

1 = Enable PMU interrupt from MRING

OnEvt Interrupt MASK PMU Interrupt Enable

When reads,

0 = Disable PMU interrupt from nPMWAKEUP

1 = Enable PMU interrupt from nPMWAKEUP

HOTSYNC Event

When reads, 0 = Not Hot Sync state; 1 = Hot Sync status

When writes, HotSync Interrupt Clear. Writing a `1' to this bit clears the event bit

WDTEvt: Watch Dog Reset (Warm reset)

When reads,

0 = No Watch dog Timer event occured

1 = A Watch dog timer event has ocurred since last cleared

When writes, Watch dog Reset Clear. Writing a `1' to this bit clears the event bit

RESETEvt: Warm RESET Event (debounced)

When reads,

0 = No Warm RESET event has occurred

1 = A Warm RESET event has occurred since last cleared

When writes, Warm Reset Clear. Writing a `1' to this bit clears the event bit.

PowerFailEvt: ADPATOR NOT OK (debounced)

When reads,

0 = No Power Fail event since last cleared

1 = A Power Fail event has occurred since last cleared

When writes, Power Fail Interrupt Clear. Writing a `1' to this bit clears a pending interrupt bit.

RTCEvt

When reads,

0 = No Real Time Clock (RTC) calendar wake-up event since last cleared

1 = Real Time Clock (RTC) calendar wake-up event since last cleared

When writes, RTC Interrupt Clear. Writing a `1' to this bit clears a pending interrupt bit.

RIEvt (debounced)

When reads,

0 = No Modem Ring Indicate wake-up event since last cleared

1 = Modem Ring Indicate wake-up event since last cleared

When writes, RI Interrupt Clear. Writing a `1' to this bit clears a pending interrupt bit.

© 2004 MagnaChip Semiconductor Ltd. All Ri3g1hts Reserved.

- 31 -

Version 1.1