ALC202 Просмотр технического описания (PDF) - Realtek Semiconductor

Номер в каталоге

Компоненты Описание

производитель

ALC202 Datasheet PDF : 42 Pages

| |||

ALC202/ALC202A

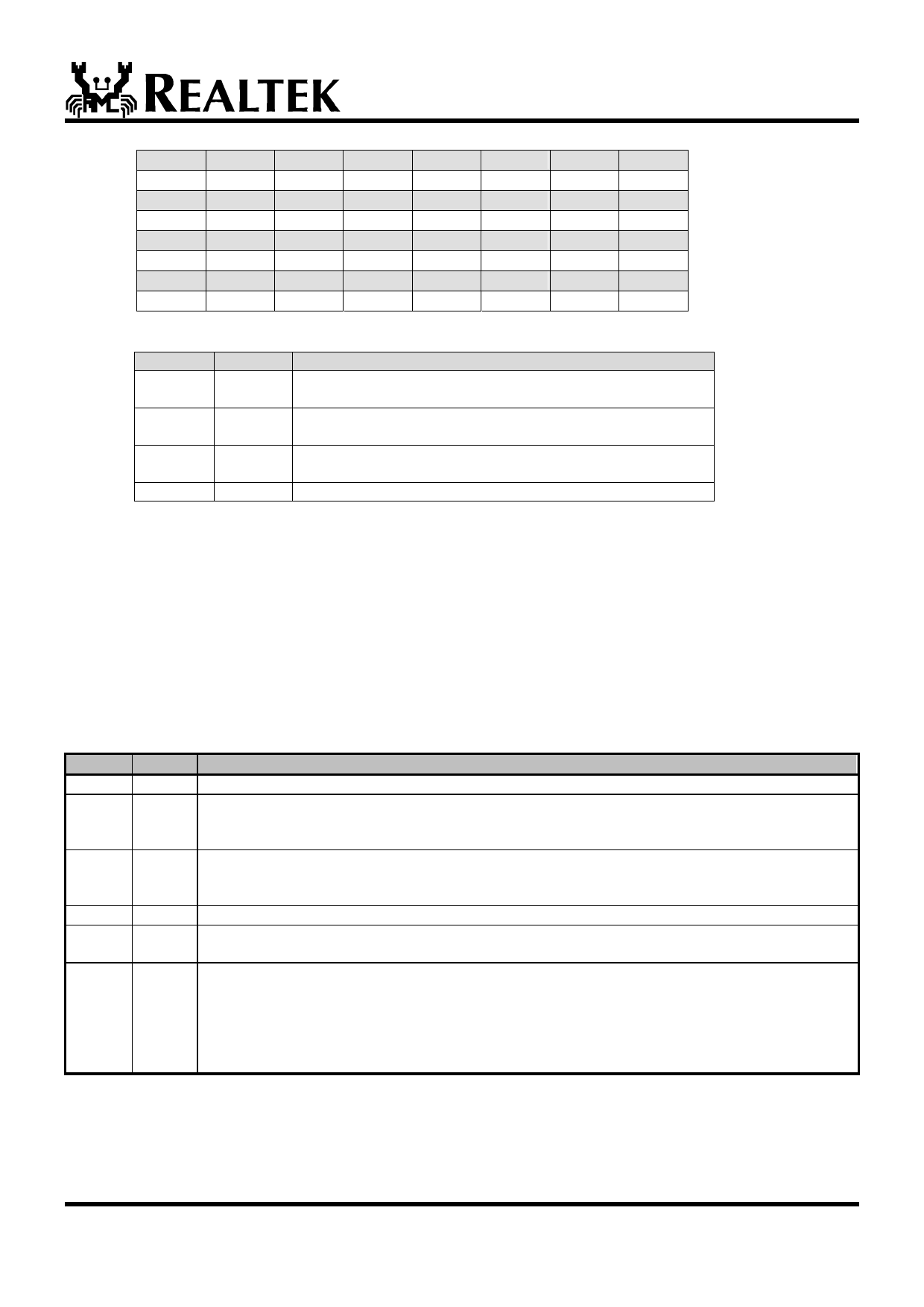

The consumer channel status block (bit0~bit31):

0

1

2

3

4

5

6

7

PRO=0 /AUDIO COPY PRE

0

0

0

0

8

9

10

11

12

13

14

15

CC0 CC1 CC2 CC3 CC4 CC5 CC6 LEVEL

16

17

18

19

20

21

22

23

0

0

0

0

0

0

0

0

24

25

26

27

28

29

30

31

Fs0

Fs1

Fs2

Fs3

0

0

0

0

The “V” bit in the sub-frame is determined by Validity control (MX3A.15) and VCFG (MX2A.15):

Validity VCFG

Operation

0

0 If S/PDIF FIFO is under-run, the “V” bit in the sub-frame is set to

indicate that the S/PDIF data is invalid.

0

1 If S/PDIF FIFO is under-run, the “V” bit in the sub-frame is always

0, and pads the data with “0”s.

1

0 The “V” bit is always 1, and data bits (bit 8 ~ bit 27) should be

forced to 0.

1

1 Reserved

6.2 Vendor Defined Registers

The ALC202 supports only one vendor defined register. This register, not defined in the AC’97 specifications, is available to

Realtek and Realtek customers for specialized functions.

6.2.1 MX6A Miscellaneous Control

Default: 0000h

The default source of S/PDIF output is data sent by controller. When bit 12 is set, S/PDIF data comes from the ADC of the

ALC202. To keep data concurrence, software must guarantee that the sample rates in MX32 and MX3A[13:12] are the same.

SPCV is no longer a validity for S/PDIF configuration. If software does not keep the same sample rates, the S/PDIF output will

be auto forbidden by hardware, and undefined consequences may occur.

Bit Type

Function

15:14

13

12

11:4

3

2:0

Reserved

R/W DAC PCM(n+1) Slot# Select (When DRA=1)

1: PCM(n+1) captured from Slot-7/8

0: PCM(n+1) captured from Slot-10/11. (Default in AC’97 rev2.2)

R/W S/PDIF Source:

1: S/PDIF data is from ADC

0: S/PDIF data is from controller (default)

Reserved

R/W SPDIF Out Volume Control – Mute Bit:

1: Clamp SPDIF output data to 0. (Mute) 0: Normal

R/W SPDIF Out Volume Control – In 6 dB Step Attenuation:

000: 0dB

001: -6dB

010: -12dB

…

111: -42dB

2002/07/30

20

Rev.1.28