ALC202 Просмотр технического описания (PDF) - Realtek Semiconductor

Номер в каталоге

Компоненты Описание

производитель

ALC202 Datasheet PDF : 42 Pages

| |||

ALC202/ALC202A

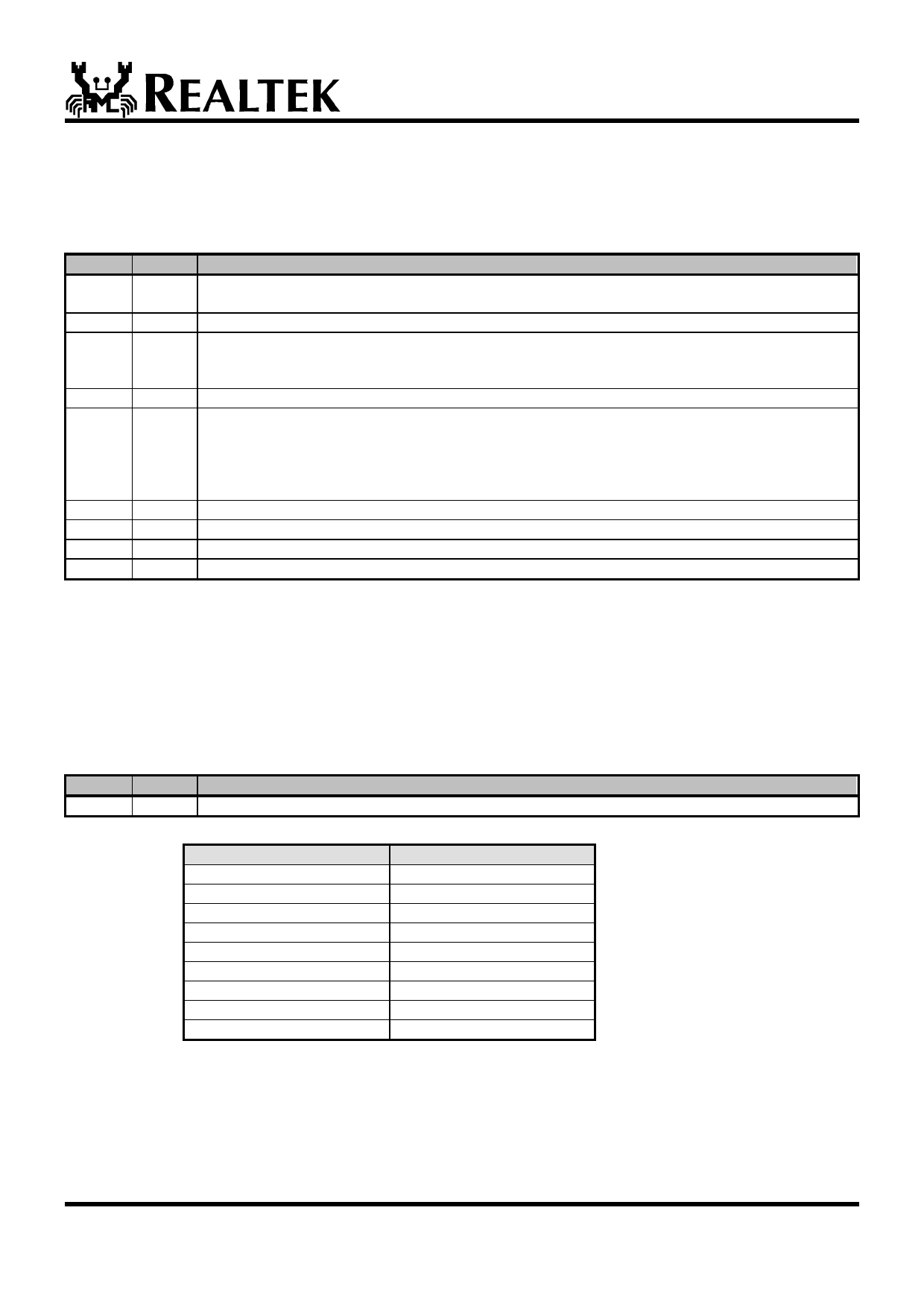

6.1.19 MX2A Extended Audio Status and Control

Default: 0000h

This register contains two active bits for powerdown and status of the surrounding DACs. Bits 0, 1 & 2 are read/write bits which

are used to enable or disable VRA, DRA and SPDIF respectively. Bits 4 & 5 are read/write bits used to determine the AC-LINK

slot assignment of the S/PDIF. Bit 10 is a read only bit which tells the controller if the S/PDIF configuration is valid.

Bit Type

Function

15

14:11

10

9:6

5:4

3

2

1

0

R/W Validity Configuration of S/PDIF Output: (VCFG)

Combines with MX3A.15 to decide validity control in S/PDIF output signal.

NA Reserved

R S/PDIF Configuration Valid: (SPCV)

1: Current S/PDIF configuration {SPSA,SPSR,DAC/slot rate} is valid

0: Current S/PDIF configuration {SPSA,SPSR,DAC/slot rate} is not valid

Reserved

R/W S/PDIF Slot Assignment: (SPSA[1:0])

00: S/PDIF source data assigned to AC-LINK slot3/4

01: S/PDIF source data assigned to AC-LINK slot7/8 (Default when ID=00)

10: S/PDIF source data assigned to AC-LINK slot6/9 (Default when ID=01,10)

11: S/PDIF source data assigned to AC-LINK slot10/11 (Default when ID=11)

Reserved

R/W SPDIF: 1: Enable 0: Disable (SPDIFO is in high impedance)

R/W DRA: 1: Enable 0: Disable

R/W VRA: 1: Enable 0: Disable

If VRA = 0, ALC202 ADC/DAC operate at fixed 48KHz sampling rate. Otherwise, it operates with variable

sampling rate defined in MX2C and MX32. VRA also control write operation of MX2Cand MX32.

DRA can be written when (ID=00)&(DSA=00), otherwise it is always 0.

If DRA = 1, DAC operates at a fixed 96KHz sampling rate. The PCM(n) and PCM(n+1) data is captured in the same

frame. In this mode, MX2C is fixed at BB80h, MX32 and ADC is still controlled by VRA.

6.1.20 MX2C PCM DAC Rate

Default: BB80h

The ALC202 allows adjustment of the front center output sample rate. This register is used to adjust the sample rate. By

changing the values, sampling rates from 8000 to 48000 can be chosen.

Bit Type

Function

15:0 R/W Output Sampling Rate: FOSR[15:0]

The ALC202 supports the following sampling rates, as required in the PC99/PC2001 design guide.

Sampling rate

FOSR[15:0]

8000

1F40h

11025

2B11h

12000

2EE0

16000

3E80h

22050

5622h

24000

5DC0

32000

7D00h

44100

AC44h

48000

BB80h

Note that If the value written is not support, the closest value is returned.

When MX2A.0=0 (VRA is disable), this register will return BB80h when read.

2002/07/30

18

Rev.1.28