MT90737 Просмотр технического описания (PDF) - Mitel Networks

Номер в каталоге

Компоненты Описание

производитель

MT90737 Datasheet PDF : 40 Pages

| |||

Preliminary Information

CMOS MT90737

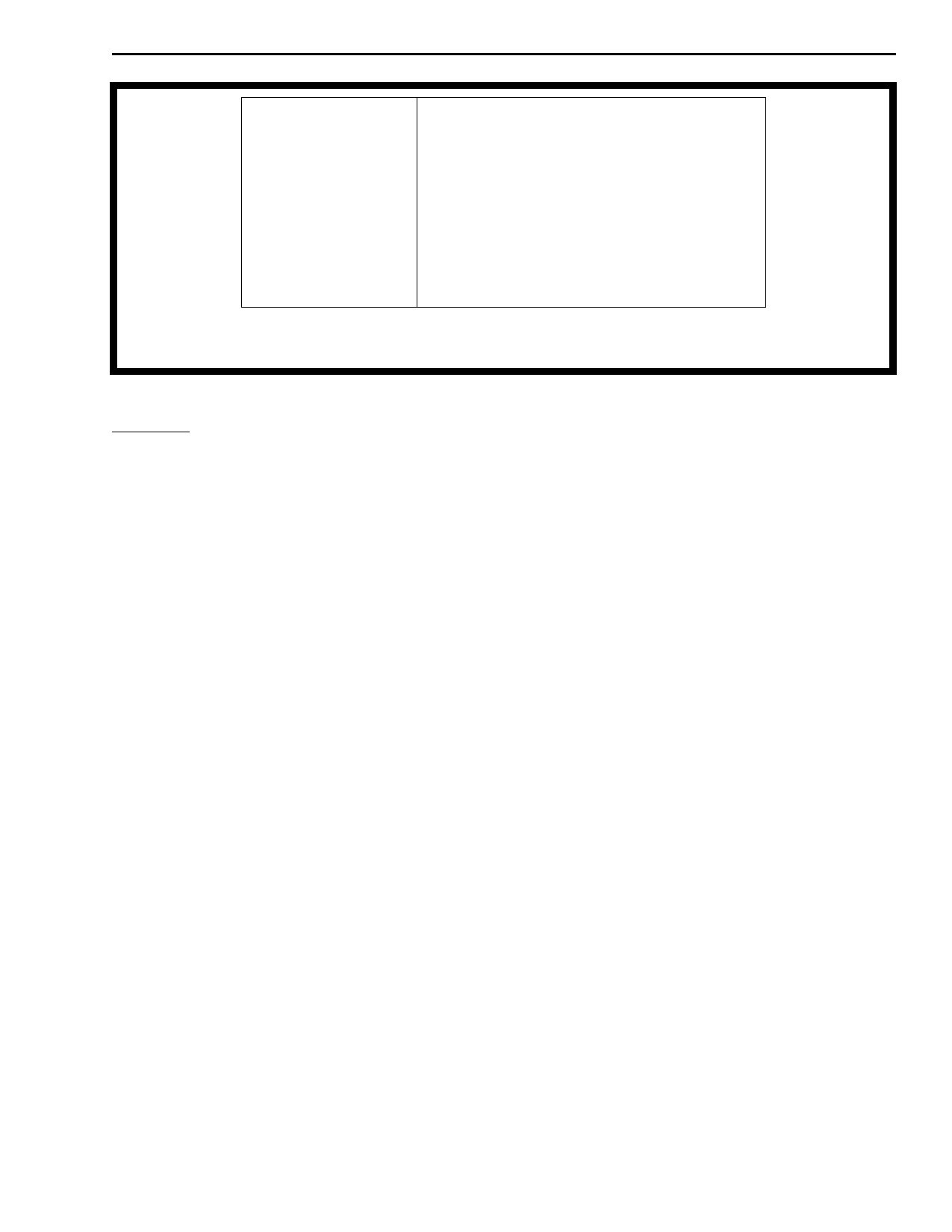

C1

C4*

C7

C10

C13*

C16*

C19*

C2*

C5*

C8

C11

C14*

C17*

C20*

C3**

C6*

C9

C12

C15*

C18*

C21*

C1 = C-bit parity mode

C2 = Reserved

C3 = Far End Alarm & Control (FEAC)

Not defined, set to one

C-Parity bits (CP-bits)

Far End Block Error (FEBE)

Maintenance data link (28 Kbit/s)

Not defined, set to one

Not defined, set to one

*These bits are provided at the C-bit interface in the C-bit mode

** Always provided at the receive C-bit interface in the C-bit mode

Figure 2 - C-Bit Assignments In C-bit Parity Format

M13 Mode

In the M13 mode, fixed DS2 to DS3 stuffing is used for

M23 multiplexing at a rate of seven stuffs per every 18

DS3 stuff opportunities. This yields a DS2 frequency of

+2.6 ppm above the desired frequency of 6.312 Mbit/s.

Adding this to the tolerance of the DS3 clock signal,

±20 ppm, the frequency is still within the ±32 ppm

allowed for a DS2 signal.

Other functions, which are common to the C-bit parity

and M13 mode, provided by the MT90737 are as fol-

lows. Under software control, the MT90737 can gener-

ate DS3 idle and AIS signals, and loop back the

transmitted DS3 signal to the receiver for test pur-

poses. The MT90737 also provides DS1 loopback

capability, and transmit clock failure protection.

Demultiplex (Receive)

In the receive direction, DS3 data (DS3DR) is clocked

into the MT90737 on positive transitions of the DS3

input clock (DS3CR). The DS3 Frame Sync Block

searches for and locks to the DS3 frame. The receive

DS3 signal is monitored for out of frame, loss of signal,

DS3 AIS, DS3 idle signal, P-bit parity, the state of the

X-bits, and loss of clock. The DS3 AIS detection mech-

anism is software selectable, with a choice of six differ-

ent patterns. These range from full compliance to

T1.107/107a to unframed all ones AIS detection. Con-

trol bits are also provided in memory which allows all,

some of, or none of the DS3 alarms to cause the inser-

tion of AIS into the receive DS1 channels.

In the C-bit parity mode, the C-bits are allocated for

network performance. The MT90737 performs Far End

Alarm and Control (FEAC) detection, C-bit parity error

detection, and Far End Block Error (FEBE) detection.

FEAC loopback requests and alarm/status information

is provided in the memory map. A receive C-bit inter-

face is provided for extraction of 14 C-bits (C2, C3,

C4, C5, C6, C13, C14, C15, C16, C17, C18, C19, C20,

and C21). The receive C-bit interface consists of a

serial data output (CDR), an output clock signal

(CCKR), a framing pulse (CFMR), and a data link indi-

cator pulse (CDCCR). The data link indicator pulse

identifies the location of the data link C-bits, C13, C14,

and C15.

In the M13 mode, destuffing from DS3 to DS2 is per-

formed based on the states of the C-bits in the DS3

subframes. If two or three of the C-bits in a subframe

are ones, the associated stuff bit is interpreted as

being a stuff bit and is removed from the data stream

and discarded.

The MT90737 synchronizes and extracts the 28 DS1

channels from the seven DS2 channels. Each of the

DS2 channels is monitored for out of frame. The

MT90737 may generate AIS in each of the DS1 signal

tributaries corresponding to the DS2 channel(s) that

lost frame, depending on the DS1 AIS alarm insertion

control bits. DS2 to DS1 destuffing is based on the

states of the three C-bits in each DS2 subframe. If two

or three of the C-bits in one of the DS2 subframes are

ones, the stuff bit for that subframe is discarded. In the

M13 mode, the DS2 C-bits or stuffing bits are also

used for DS1 remote loopback requests. The

MT90737 provides control bits in the memory map for

selecting the remote loopback detection mechanism.

The destuffing operation is still active during loopback

request and operation. In addition to DS2 synchroniza-

tion, destuffing, and remote loopback detection, the

MT90737 also extracts the X-bits from seven DS2

frames.

An option is provided that allows the received or trans-

mitted DS1 channels to be monitored for loss of signal.

Receive data for each of the DS1 channels (DRn) is

clocked out of the MT90737 on positive transitions of

the associated clock signal (CRn). In addition, the

5-73