WM8750CJLGEFL Просмотр технического описания (PDF) - Wolfson Microelectronics plc

Номер в каталоге

Компоненты Описание

производитель

WM8750CJLGEFL Datasheet PDF : 61 Pages

| |||

Production Data

SIGNAL TIMING REQUIREMENTS

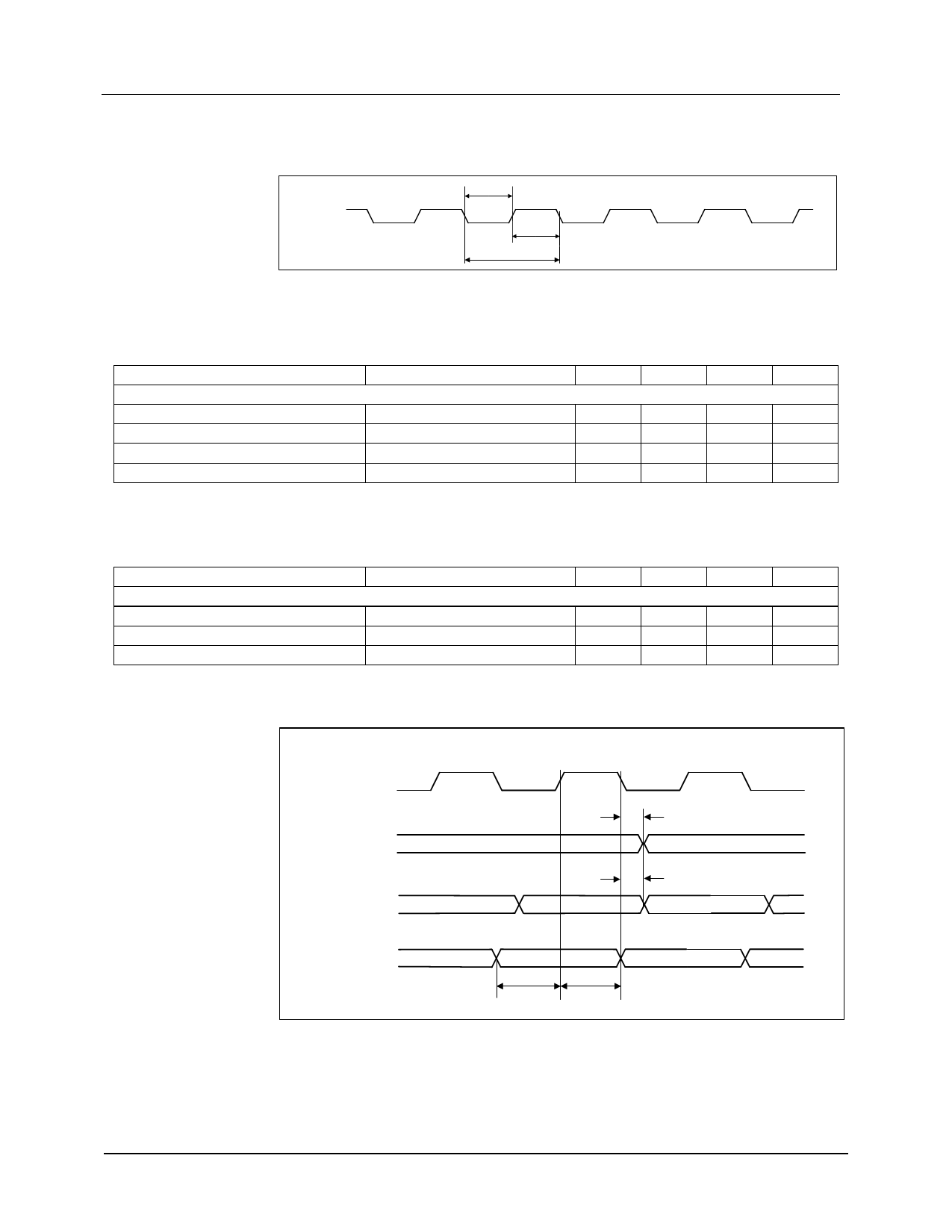

SYSTEM CLOCK TIMING

MCLK

tMCLKL

tMCLKH

tMCLKY

WM8750JL

Figure 1 System Clock Timing Requirements

Test Conditions

CLKDIV2=0, DCVDD = 1.42V, DBVDD = 3.3V, DGND = 0V, TA = +25oC, Slave Mode fs = 48kHz, MCLK = 384fs, 24-bit data,

unless otherwise stated.

PARAMETER

SYMBOL

MIN

TYP

MAX

UNIT

System Clock Timing Information

MCLK System clock pulse width high

MCLK System clock pulse width low

MCLK System clock cycle time

MCLK duty cycle

TMCLKL

TMCLKH

TMCLKY

TMCLKDS

21

21

54

60:40

ns

ns

ns

40:60

Test Conditions

CLKDIV2=1, DCVDD = 1.42V, DBVDD = 3.3V, DGND = 0V, TA = +25oC, Slave Mode fs = 48kHz, MCLK = 384fs, 24-bit data,

unless otherwise stated.

PARAMETER

SYMBOL

MIN

TYP

MAX

UNIT

System Clock Timing Information

MCLK System clock pulse width high

TMCLKL

10

ns

MCLK System clock pulse width low

TMCLKH

10

ns

MCLK System clock cycle time

TMCLKY

27

ns

AUDIO INTERFACE TIMING – MASTER MODE

BCLK

(Output)

ADCLRC/

DACLRC

(Outputs)

ADCDAT

tDL

tDDA

DACDAT

tDST

tDHT

Figure 2 Digital Audio Data Timing – Master Mode (see Control Interface)

w

PD, April 2012, Rev 4.1

11