ADV7611BSWZ-P Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

ADV7611BSWZ-P Datasheet PDF : 16 Pages

| |||

Data Sheet

ADV7611

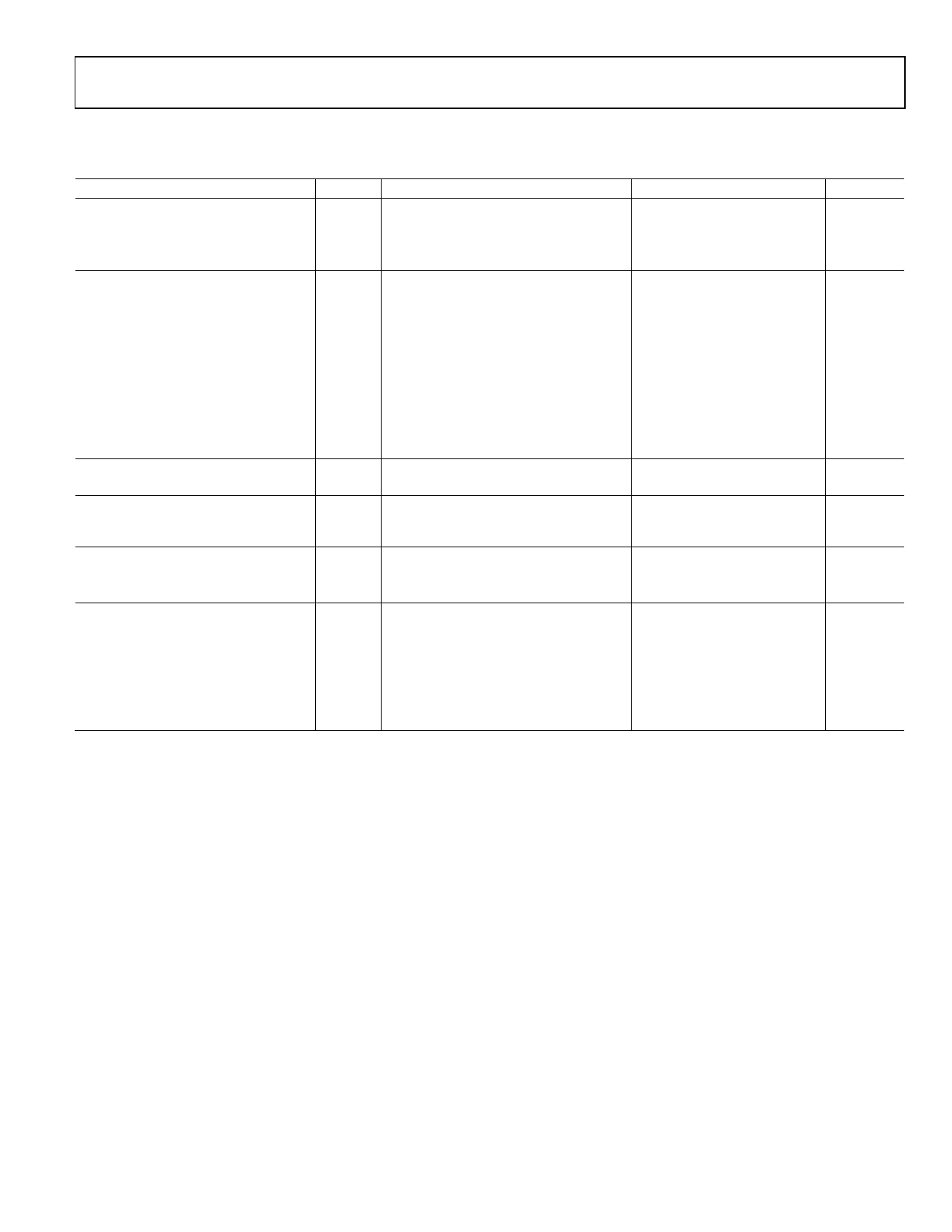

DATA AND I2C TIMING CHARACTERISTICS

Table 2.

Parameter

CLOCK AND CRYSTAL

Crystal Frequency, XTALP

Crystal Frequency Stability

LLC Frequency Range1

I2C PORTS

SCL Frequency

SCL Minimum Pulse Width High2

SCL Minimum Pulse Width Low2

Start Condition Hold Time2

Start Condition Setup Time2

SDA Setup Time2

SCL and SDA Rise Time2

SCL and SDA Fall Time2

Stop Condition Setup Time2

RESET FEATURE

Reset Pulse Width

CLOCK OUTPUTS

LLC Mark-Space Ratio2

Symbol Test Conditions/Comments

t1

t2

t3

t4

t5

t6

t7

t8

t9:t10

DATA AND CONTROL OUTPUTS3

Data Output Transition Time2, 4

I2S PORT, MASTER MODE

SCLK Mark-Space Ratio2

t11

t12

t15:t16

End of valid data to negative clock edge

Negative clock edge to start of valid data

LRCLK Data Transition Time2

LRCLK Data Transition Time2

I2S Data Transition Time2, 5

I2S Data Transition Time2, 5

t17

End of valid data to negative SCLK edge

t18

Negative SCLK edge to start of valid data

t19

End of valid data to negative SCLK edge

t20

Negative SCLK edge to start of valid data

1 Maximum LLC frequency is limited by the clock frequency of UXGA 60 Hz at 8 bit.

2 Data guaranteed by characterization.

3 With the DLL block on output clock bypassed.

4 DLL bypassed on clock path.

5 I2S is accessible via the AP pin.

Min

13.5

600

1.3

600

600

100

0.6

5

45:55

45:55

Typ

Max

28.63636

±50

165

400

300

300

55:45

1.0

2.2

0.0

0.3

55:45

10

10

5

5

Unit

MHz

ppm

MHz

kHz

ns

μs

ns

ns

ns

ns

ns

μs

ms

% duty

cycle

ns

ns

% duty

cycle

ns

ns

ns

ns

Rev. D | Page 5 of 16