AD9874 Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

AD9874 Datasheet PDF : 40 Pages

| |||

AD9874

(VDDI = VDDF = VDDA = VDDC = VDDL = VDDD = VDDH = VDDx, VDDQ = VDDP = 5.0 V, fCLK = 18 MSPS, fIF = 109.56 MHz, fLO = 107.4 MHz,

TA = 25؇C, LO = –5 dBm, LO and CLK Synthesizer Disabled, 16-Bit Data with AGC and DVGA enabled, unless otherwise noted.)1

10.0

16-BIT

9.5 I/Q DATA

9.0

16-BIT

I/Q DATA

w/ DVGA

ENABLED

10.0

9.5

16-BIT

DATA

9.0

16-BIT DATA

w/ DVGA

ENABLED

10.0

16-BIT DATA

w/ DVGA

ENABLED

9.5

16-BIT

DATA

9.0

24-BIT

DATA

8.5

8.5

8.5

8.0

24-BIT

I/Q DATA

7.5

10

100

CHANNEL BANDWIDTH – kHz

1000

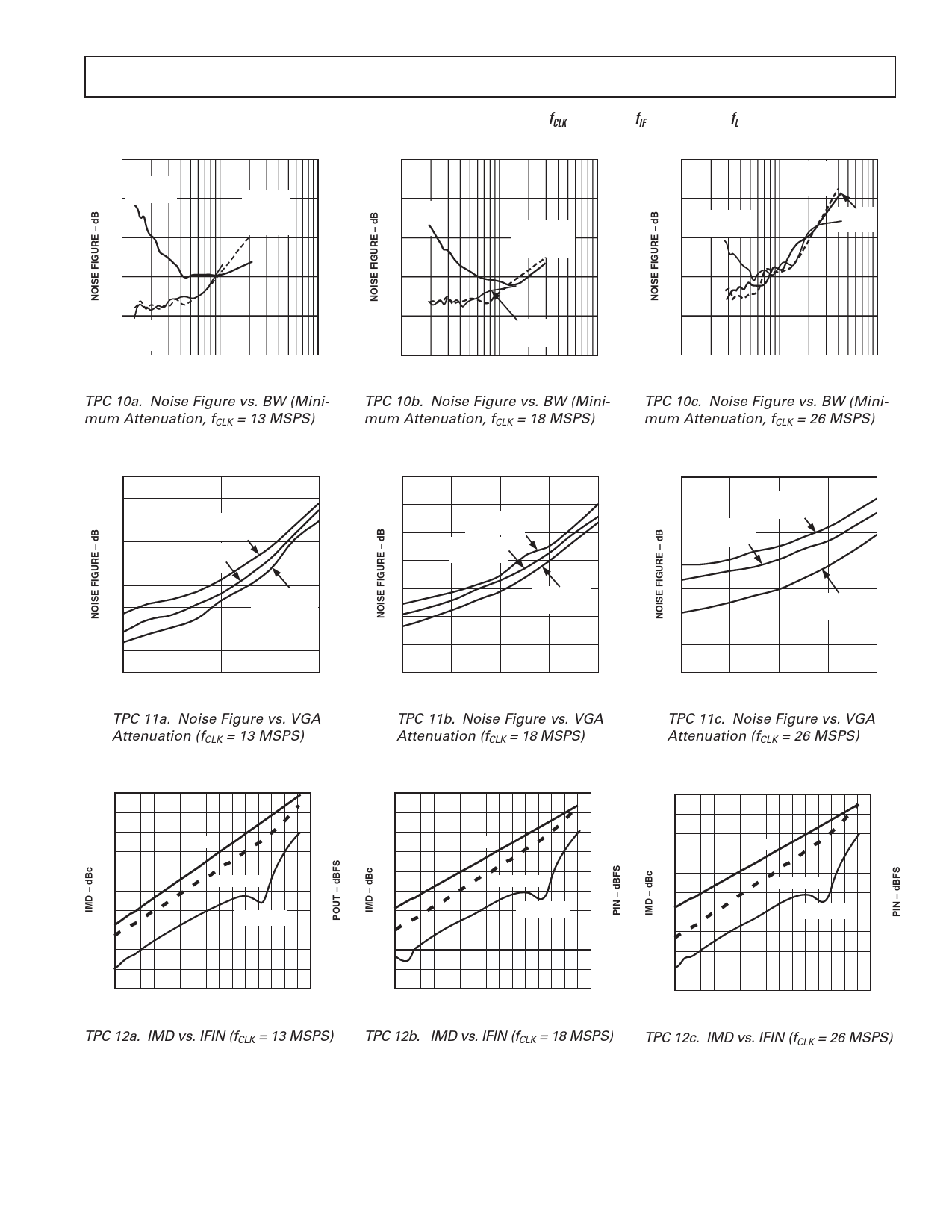

TPC 10a. Noise Figure vs. BW (Mini-

mum Attenuation, fCLK = 13 MSPS)

8.0

7.5

10

24-BIT

DATA

100

CHANNEL BANDWIDTH – kHz

1000

TPC 10b. Noise Figure vs. BW (Mini-

mum Attenuation, fCLK = 18 MSPS)

8.0

7.5

10

100

CHANNEL BANDWIDTH – kHz

1000

TPC 10c. Noise Figure vs. BW (Mini-

mum Attenuation, fCLK = 26 MSPS)

11.5

11.0

10.5

BW = 27.08kHz

(K = 0, M = 3)

10.0

BW = 12.04kHz

9.5

(K = 0, M = 8)

9.0

BW = 6.78kHz

8.5

(K = 0, M = 15)

8.0

7.5

7.0

0

3

6

9

12

VGA ATTENUATION – dB

TPC 11a. Noise Figure vs. VGA

Attenuation (fCLK = 13 MSPS)

14

13

BW = 75kHz

12

(K = 0, M = 1)

BW = 50kHz

11

(K = 0, M = 2)

10

BW = 15kHz

(K = 0, M = 9)

9

8

7

0

3

6

9

12

VGA ATTENUATION – dB

TPC 11b. Noise Figure vs. VGA

Attenuation (fCLK = 18 MSPS)

14

13

BW = 135.42kHz

(K = 1, M = 1)

12 BW = 90.28kHz

(K = 1, M = 2)

11

10

BW = 27.08kHz

9

(K = 1, M = 9)

8

7

0

3

6

9

12

VGA ATTENUATION – dB

TPC 11c. Noise Figure vs. VGA

Attenuation (fCLK = 26 MSPS)

–30

–5

–40

–10

–50

PIN

–15

–60

–70

–20

LOW BIAS

–80

–25

–90

–100

–110

–120

HIGH BIAS

–30

–35

–40

–130

–45

–45 –42 –39 –36 –33 –30 –27 –24

IFIN – dBm

TPC 12a. IMD vs. IFIN (fCLK = 13 MSPS)

–30

–5

–40

–10

–50

PIN

–15

–60

–70

–20

LOW BIAS

–80

–25

–90

–100

–110

–120

HIGH BIAS

–30

–35

–40

–130

–45

–45 –42 –39 –36 –33 –30 –27 –24

IFIN – dBm

TPC 12b. IMD vs. IFIN (fCLK = 18 MSPS)

–30

–5

–40

–10

–50

PIN

–15

–60

–70

–20

LOW BIAS

–80

–25

–90

–100

–110

–120

HIGH BIAS

–30

–35

–40

–130

–45

–45 –42 –39 –36 –33 –30 –27 –24

IFIN – dBm

TPC 12c. IMD vs. IFIN (fCLK = 26 MSPS)

1Data taken with Toko FSLM series 10 µH inductors.

2High Bias corresponds to LNA_Mixer Setting of 33 in SPI Register 0x01.

3Low Bias corresponds to LNA_Mixer Setting of 12 in SPI Register 0x01.

REV. A

–11–