GS8180Q18D(2002) Просмотр технического описания (PDF) - Giga Semiconductor

Номер в каталоге

Компоненты Описание

производитель

GS8180Q18D Datasheet PDF : 29 Pages

| |||

Preliminary

GS8180Q18/36D-200/167/133

weighted impedance steps. Impedance updates for “0s” occur whenever the SRAM is driving “1s” for the same DQs (and vice-versa for “1s”) or

the SRAM is in HI-Z. The SRAM requires 32K start-up cycles, selected or deselected, after VDD reaches its operating range to reach its

programmed output driver impedance.

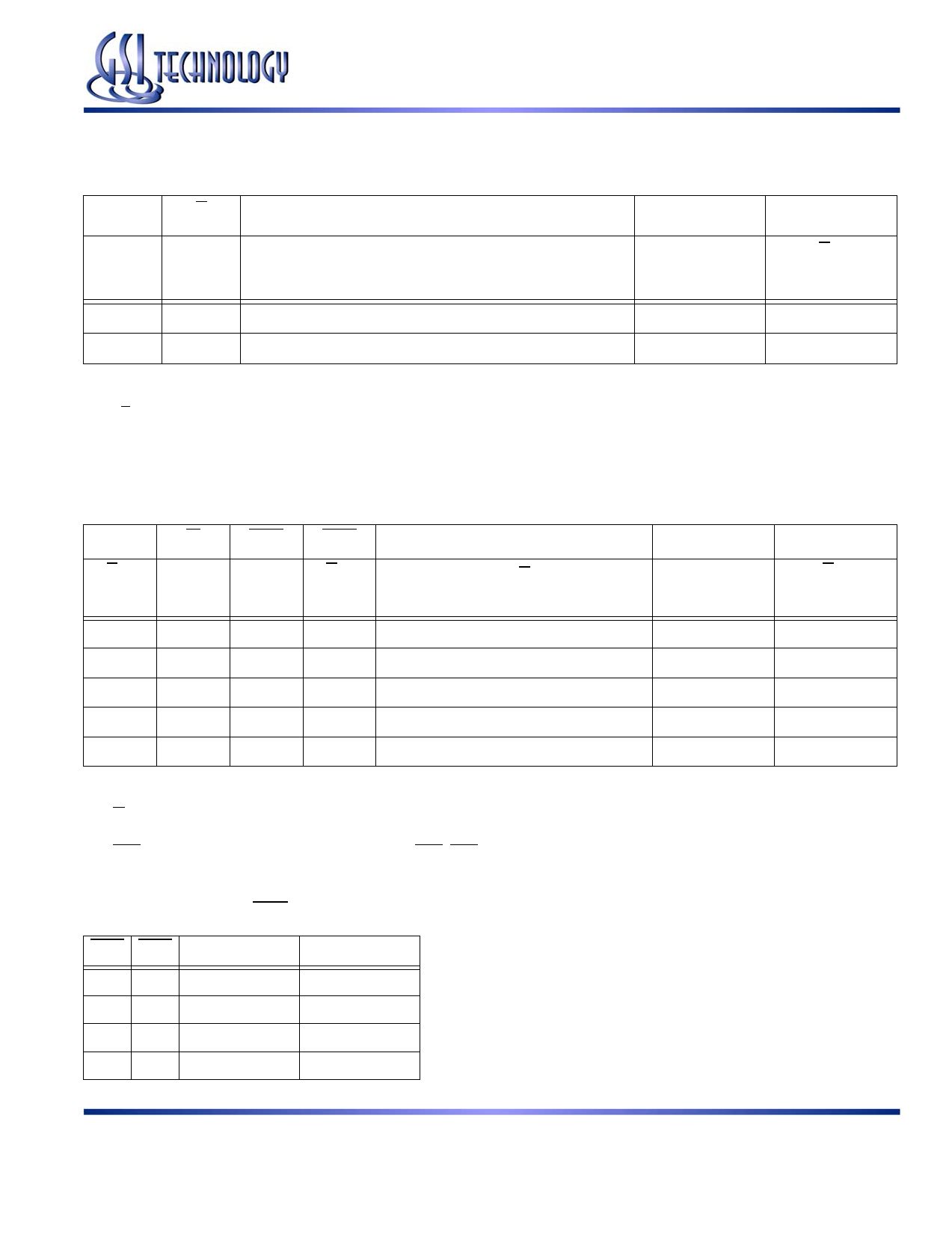

Σ2x2B2 Coherency and Pass Through Functions

Because the Σ2x2B2 read and write commands are loaded at the same time, there may be some confusion over what constitutes “coherent”

operation. Normally, one would expect a RAM to produce the just-written data when it is read immediately after a write. This is true of the

Σ2x2B2 except in one case, as is illustrated in the following diagram. If the user holds the same address value in a given K clock cycle, loading

the same address as a read address and then as a matching write address, the Σ2x2B2 will read or “Pass-thru” the latest data input, rather than

the data from the previously completed write operation.

Dwg Rev. G

Read

K

Σ2x2B2 Coherency and Pass Through Functions

Write

Read

Write

Read

Write

Read

Write

/K

A

B

C

D

E

F

G

H

I

Address

OO

OI

OI

OO

OO

OO

OI

IO

OO

/R

/W

/BWx

DB0

DB1

DD0

DD1

DF0

DF1

DH0

DH1

DI0

D

5

6

8

2

7

1

9

3

4

C

COHERENT

PASS-THRU

/C

QA0

QA1

QC0

QC1

QE0

QE1

Q

?

?

5

6

7

1

CQ

/CQ

Rev: 2.00f 6/2002

11/29

© 2002, Giga Semiconductor, Inc.

Specifications cited are design targets and are subject to change without notice. For latest documentation contact your GSI representative.