HMS30C7202N Просмотр технического описания (PDF) - MagnaChip Semiconductor

Номер в каталоге

Компоненты Описание

производитель

HMS30C7202N Datasheet PDF : 179 Pages

| |||

HMS30C7202N

T7 Rising LCP to Display Data Change TBD

TBD

ns

T8

VSYNC Width

1

64 tHperiod(Notes)

T9

VSYNC Back-Porch

1

256

tHperiod

T10

VSYNC Front-Porch

1

256

tHperiod

T11

HSYNC Width

1

256

tCLK

T12

HSYNC Back-Porch

1

- 256

tCLK

T13

HSYNC Front-Porch

1

- 256

tCLK

T14

Dot Clock Period

1

-

-

tCLK

LCD Interface Signal Timing Parameters

Note : tCLK is BCLK or VCLK(LCD Controller Internal Clock Source : 31.5 or 40 MHz).

tHperiod Max = 1408 tCLK

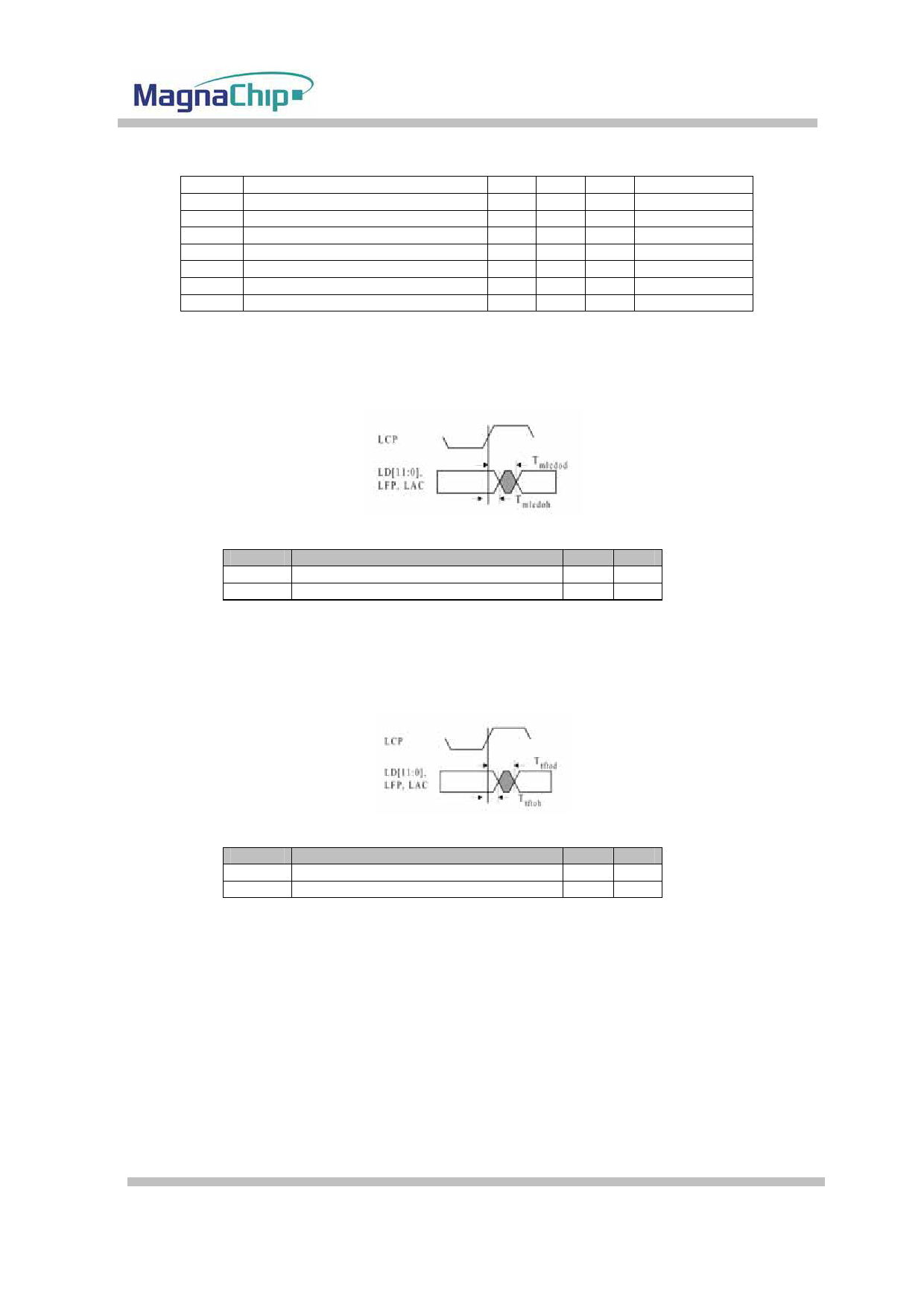

STN Mode Signal Delay

Symbol

Tmlcdod

Tmlcdoh

Parameter

Min Max

Output Delay Time from LCP rising

-

5

Output Hold Time from LCP Rising

-

-5

STN Mode Signal Delay Parameters

Timing values are derived from simulations using 0pF signal loading.

Actual circuit output delays should be calculated by adding

manufacturers signal load de-rating delay values.

TFT Mode Signal Delay

Symbol

Ttftod

Ttftoh

Parameter

Min Max

Output Delay Time from LCP rising

-

3

Output Hold Time from LCP Rising

-

-3

TFT Mode Signal Delay Parameters

Timing values are derived from simulations using 0pF signal loading.

Actual circuit output delays should be calculated by adding

manufacturers signal load de-rating delay values.

© 2004 MagnaChip Semiconductor Ltd. All R1ig70hts Reserved.

- 170 -

Version 1.1