DS21Q554 Просмотр технического описания (PDF) - Dallas Semiconductor -> Maxim Integrated

Номер в каталоге

Компоненты Описание

производитель

DS21Q554

DS21Q554 Datasheet PDF : 13 Pages

| |||

DALLAS SEMICONDUCTOR DS21Q352/DS21Q552/DS21Q354/DS21Q554 Preliminary Data Sheet

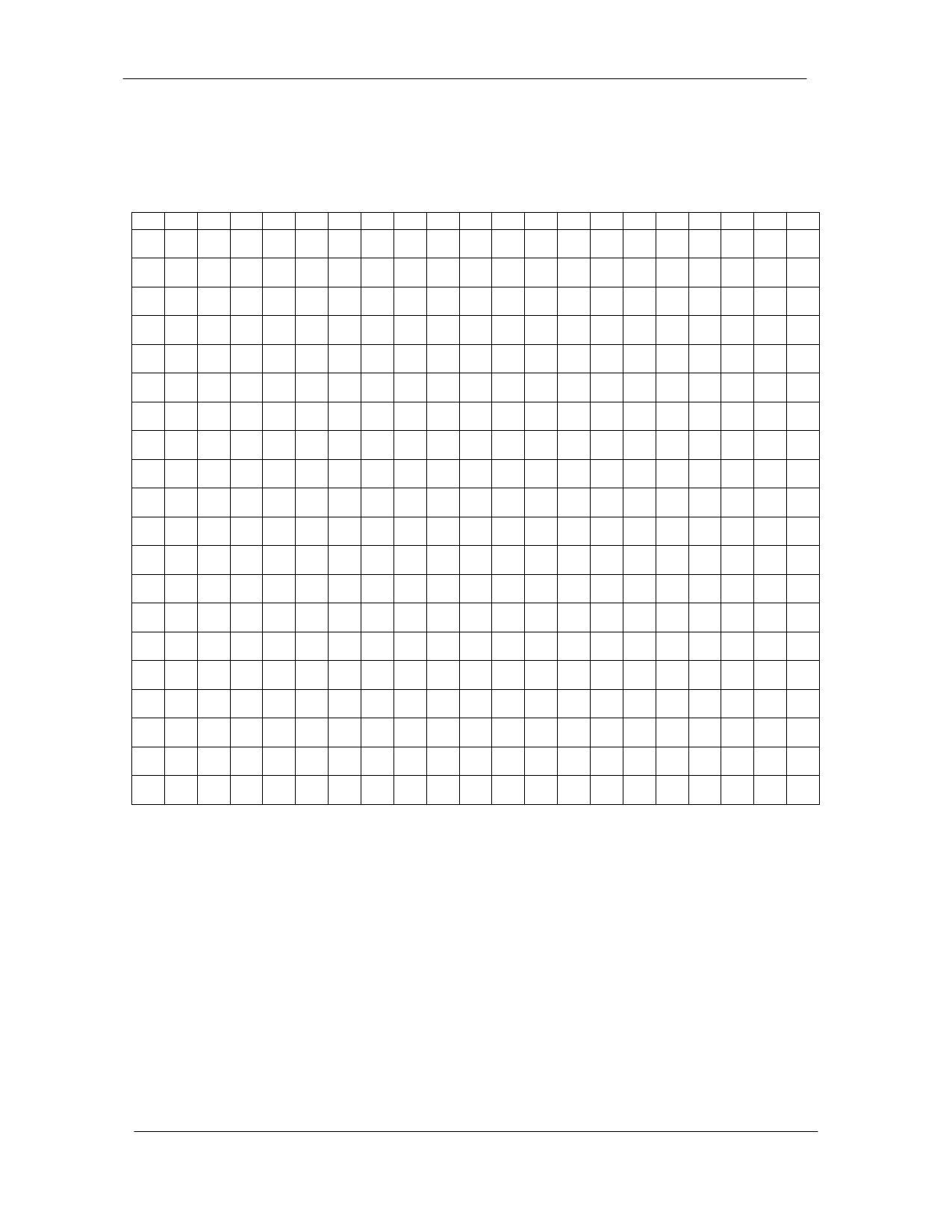

DS21Q352 / DS21Q552 / DS21Q354 / DS21Q554 PCB Land Pattern Figure 2

The diagram shown below is the lead pattern that will be placed on the target PCB. This is the same

pattern that would be seen as viewed through the MCM from the top.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

A

rneg

rf

i

sync

rlink

3

rclk

i

dvss

3

co

3

tclko

tpos

dvdd

tsig

tsys

rlclk

rlink

3

i

3

3

clk

3

2

cs

2*

rclki

rpos

dvss

tch

tsys

dvss

2

o

2

clk

clk

2

3

3

3

3

3

2

2

2

B

rpos rposi dvdd

o

3

3

rclk

o

3

3

cs

dvdd dvss

tch

dvss

tclk

dvss

dvdd

rclk

rpos rneg

rsig

3*

3

3

clk

3

3

2

2

2

i

o

2

3

2

2

co

ts

tclk

tneg

2

sync

2

o

2

2

C

rsig

rneg

dvss dvdd

tvss

tlink tsync

tclk

3

o

3

3

3

3

3

i

tpos

o

tser

3

tch

blk

dvdd dvss

rclk

2

2

o

rsigf

dvdd

tser

2

2

2

tsig

2

tpos

tpos

o

i

3

3

3

3

2

2

2

D

rsync rsigf

3

3

rlclk

3

rvss

3

rvss

3

tlclk

3

ci

3

tneg

tneg

ts

tvdd rsync rneg

rch

rser

rm

rf

dvdd

tclk

tsync

i

o

sync

3

2

i

clk

2

sync sync

2

i

2

3

3

3

2

2

2

2

2

E

rlos

3

rser

3

rclk

3

rvdd

3

rlos

tclk

tlink

tlclk

2

o

2

2

2

F

rlclk

rm

rch

1

sync

clk

8m

clk

3

3

3

rsys

ci

tneg

tch

clk

2

i

blk

2

2

2

G

rsync

1

rlink

1

rsys

clk

rch

blk

3

3

rch

tvss

tvdd

dvdd

blk

2

2

4

2

H

rsys

clk

rlos

1

dvss

1

A5

1

8m

jtdo

rvss

dvss

clk

2

2

4

2

J

rch

rser

dvdd

dvss

clk

1

1

1

1

rvdd

rvss

D1/

co

2

2

AD1

4

K

rsigf

1

liuc

wr*

rf

sync

1

cs

rlclk

ts

tser

4*

4

sync

4

4

L

rm

sync

rsig

1

rneg

rpos

o

o

1

1

1

A1

tch

tsig

dvss

clk

4

4

4

M

8m

clk

rch

blk

rclk

o

rclk

i

1

1

1

1

dvdd

rclk

4

4

tclk

dvdd

4

4

N

jtdi

rd*

rclk

dvdd

1

1

dvss

tsys

tpos

tneg

4

clk

o

o

4

4

4

P

rvdd

1

bts

cs

1*

A7/

ALE

rneg

dvdd

tclk

tclk

i

4

o

i

4

4

4

R

tneg

i

rvss

1

rneg

i

rpos

i

1

1

1

rclk

tsync tpos

tneg

i

4

i

i

4

4

4

T

mclk

rvss

tneg

1

1

o

A3

1

rclk

tlclk

tlink

ci

o

4

4

4

4

U

int*

dvdd

1

A0

D7/

D5/

dvss

D3/

AD7

AD5

1

AD3

A6

D4/

mux

D0/

rlink

dvss

AD4

AD0

4

4

rch

clk

rpos

test

rneg

tvss

tvdd

o

o

4

4

tch

blk

4

4

4

4

V

tsync

1

A2

tlclk

D6/

dvdd

tclk

tpos

1

AD6

1

i

o

A4

co

1

tch

rlos

rsync

8m

rf

rpos

rsigf

jtdo3

jtrst*

jtdo4

rvss

clk

4

4

clk

sync

i

4

4

1

1

1

4

4

4

W

tch

blk

tvdd

1

tpos

i

tvss

1

tlink

1

ci

1

tclk

dvss

tser

tsig

tsys

ts

jtms

rsys

D2/

rm

rser

rvdd

rvss

mclk

o

1

1

1

clk

sync

clk

AD2

sync

4

4

4

2

1

1

1

1

1

4

4

Y

ttip

tring

1

1

ttip

2

tring

ttip

tring

2

3

3

ttip

4

tring

tclk

4

1

rtip

rring

rch

1

1

blk

rtip

rring

jtclk

2

2

rtip

rring

rsig

3

3

4

rtip

rring

4

4

4

December 29, 1998

11