HMP8156 Просмотр технического описания (PDF) - Intersil

Номер в каталоге

Компоненты Описание

производитель

HMP8156 Datasheet PDF : 33 Pages

| |||

HMP8156

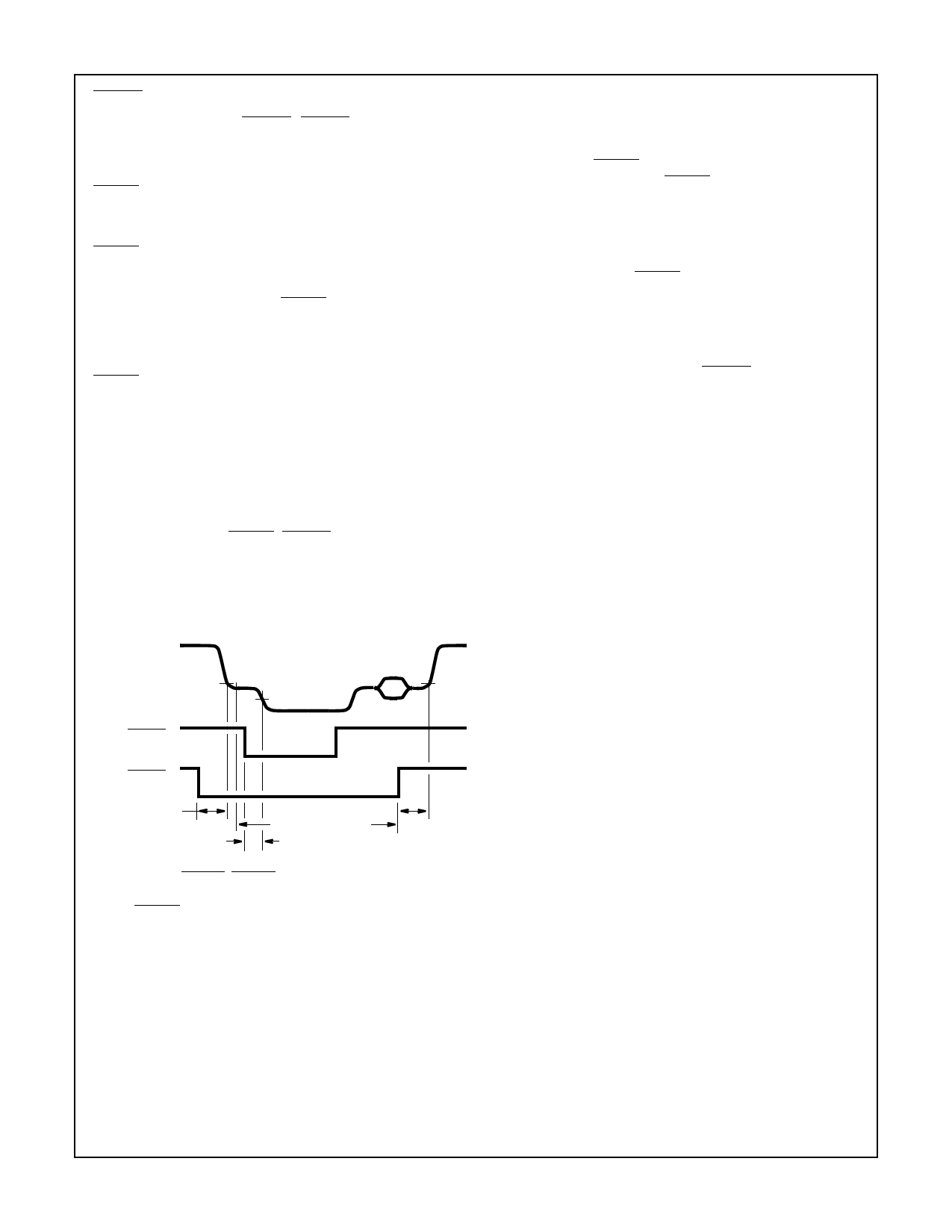

BLANK Timing

The encoder uses the HSYNC, VSYNC, FIELD signals to

generate a standard composite video waveform with no

active video. The signal includes only sync tips, color burst,

and optionally, a 7.5 IRE blanking setup. Based on the

BLANK signal, the encoder adds the pixel and overlay input

data to the video waveform.

The encoder ignores the pixel and overlay input data when

BLANK is asserted. Instead of the input data, the encoder

generates the blanking level. The encoder also ignores the

pixel and overlay inputs when generating closed captioning

data on a specific line, even if BLANK is negated.

There must be an even number of active and total pixels per

line. In the 8-bit YCbCr modes, the number of active and

total pixels per line must be a multiple of four. Note that if

BLANK is an output, half-line blanking on the output video

cannot be done.

The HMP8156 never adds a 7.5 IRE blanking setup during

the active line time on scan lines 1-21 and 263-284 for (M,

NSM) NTSC, scan lines 523-18 and 260-281 for (M) PAL,

and scan lines 623-22 and 311-335 for (N) PAL, allowing the

generation of video test signals, timecode, and other infor-

mation by controlling the pixel inputs appropriately.

The relative timing of BLANK, HSYNC, and the output video

depends on the blanking and sync I/O directions. The typical

timing relation is shown in Figure 12. The delays which vary

with operating mode are indicated. The width of the compos-

ite sync tip and the location and duration of the color burst

are fixed based on the video format.

COMPOSITE

VIDEO OUT

HSYNC

The zero count for horizontal blanking is 32 CLK2 cycles

before the 50% point of the composite sync. From this zero

point, the HMP8156 counts every other CLK2 cycle. When

the count reaches the value in the start_h_blank register, the

encoder negates BLANK. When the count reaches the value

in the end_h_blank register, BLANK is asserted. There may

be an additional 0-7 CLK2 delays in modes which use CLK.

The data pipeline delay through the HMP8156 is 26 CLK2

cycles. In operating modes which use CLK to gate the inputs

into the encoder, the delay may be an additional 0-7 CLK2

cycles. The delay from BLANK to the start or end of active

video is an additional one-half CLK cycle when the blank tim-

ing select bit is cleared. The active video may also appear to

end early or start late since the HMP8156 controls the blank-

ing edge rates.

The delay from the active edge of HSYNC to the 50% point

of the composite sync is 4-39 CLK2 cycles depending on the

HMP8156 operating mode. The delay is shortest when the

encoder is the timing master; it is longest when in slave

mode.

CLK2 Input

The CLK2 input clocks all of the HMP8156, including its

video timing counters. For proper operation, all of the

HMP8156 inputs must be synchronous with CLK2. The fre-

quency of CLK2 depends on the device’s operating mode

and the total number of pixels per line. The standard clock

frequencies are shown in Table 7.

Note that the color subcarrier is derived from the CLK2 input.

Any jitter on CLK2 will be transferred to the color subcarrier,

resulting in color changes. Just 400ps of jitter on CLK2

causes up to a 1o color subcarrier phase shift. Thus, CLK2

should be derived from a stable clock source, such as a

crystal. The use of a PLL to generate CLK2 is not recom-

mended.

BLANK

DATA PIPE

DELAY

START H BLANK

SYNC DELAY

FIGURE 12. HSYNC, BLANK, AND OUTPUT VIDEO TIMING

When BLANK is an output, the encoder asserts it during the

inactive portions of active scan lines and for all of each inac-

tive scan line. The inactive scan lines blanked each field are

determined by the start_v_blank and end_v_blank registers.

The inactive portion of active scan lines is determined by the

start_h_blank and end_h_blank registers.

11