68901N04 Просмотр технического описания (PDF) - STMicroelectronics

Номер в каталоге

Компоненты Описание

производитель

68901N04 Datasheet PDF : 33 Pages

| |||

MK68901

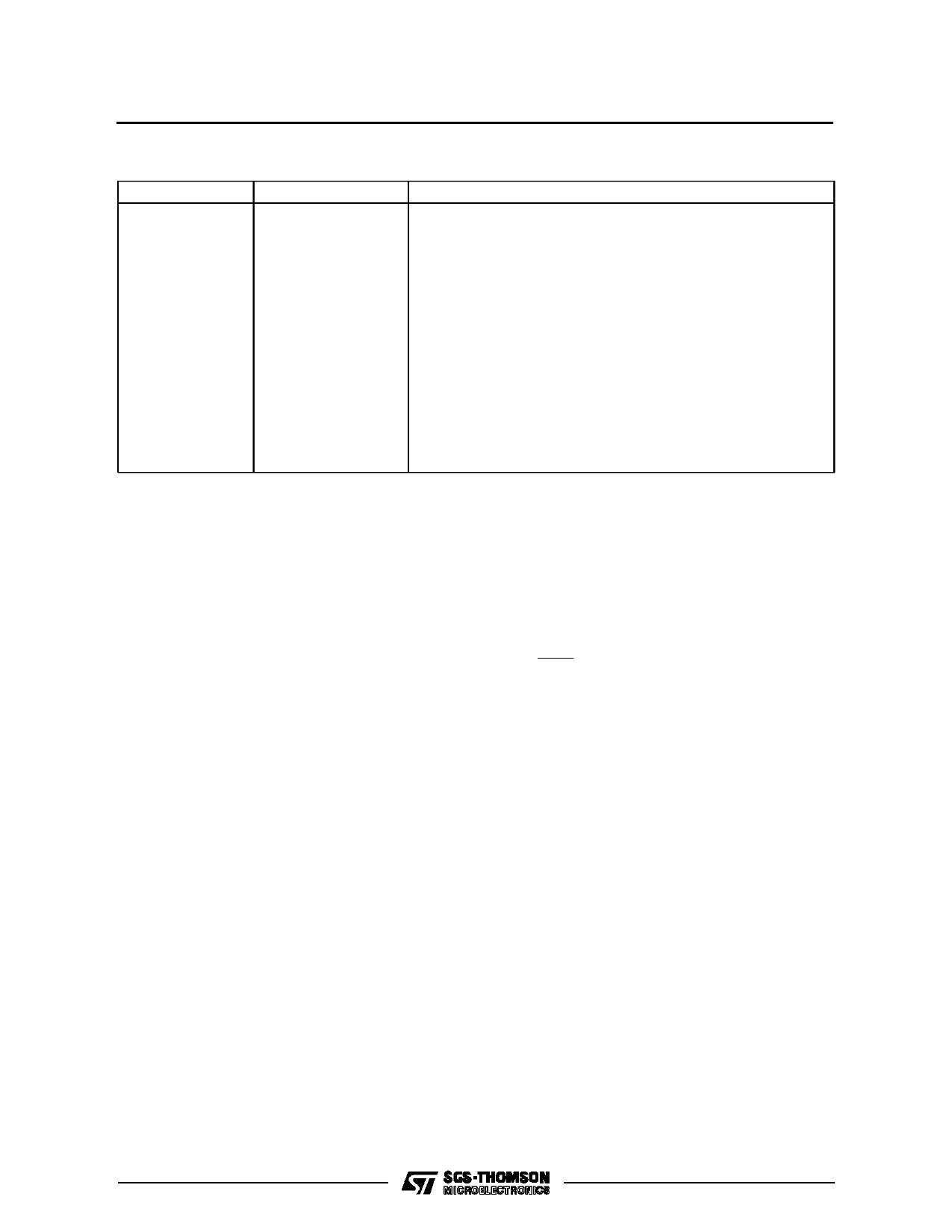

Figure 9 : Interrupt Control Register Definitions

Priority

HIGHEST

LOWEST

Channel

1111

1110

1101

1100

1011

1010

1001

1000

0111

0110

0101

0100

0011

0010

0001

0000

Description

General Purpose Interrupt 7(I7)

General Purpose Interrupt 6(I6)

Timer A

Receive Buffer Full

Receive Error

Transmit Buffer Empty

Transmit Error

Timer B

General Purpose Interrupt 5(I5)

General Purpose Interrupt 4(I4)

Timer C

Timer D

General Purpose Interrupt 3(I3)

General Purpose Interrupt 2(I2)

General Purpose Interrupt 1(I1)

General Purpose Interrupt 0(I0)

Interrupts may be either polled or vectored. Each

channel may be individual enabled or disabled by

writing a one or a zero in the appropriate bit of Inter-

rupt Enable Registers (IERA, IERB - see figure 8 for

all registers in this section). When disabled, an in-

terrupt channel is completely inactive. Any internal

or external action which would normally produce an

interrupt on that channel is ignored and any pending

interrupt on that channel will be cleared by disabling

that channel. Disabling an interrupt channel has no

effect on the corresponding bit in Interrupt In-Ser-

vice Registers (ISRA, ISRB) ; thus, if the In-service

Registers are used and an interrupt is in service on

that channel when the channel is disabled, it will re-

main in service until cleared in the normal manner.

IERA and IERB are also readable.

When an interrupt is received on an enabled chan-

nel, its corresponding bit in the pending register will

be set. When that channel is acknowledged it will

pass its vector, and the corresponding bit in the In-

terrupt Pending Register (IPRA or IRPB) will be

cleared. IPRA and IPRB are readable ; thus by pol-

ling IPRA and IPRB, it can be determined whether

a channel has a pending interrupt. IPRA and IPRB

are also writeable and a pending interrupt can be

cleared without going through the acknowledge se-

quence by writing a zero to the appropriate bit. This

allows any one bit to be cleared, without altering any

other bits, simply by writing all ones except for the

bit position to be cleared to IPRA or IPRB. Thus a

fully polled interrupt scheme is possible. Note : wri-

ting a one to IPRA, IPRB has no effect on the inter-

rupt pending register.

The interrupt mask registers (IMRA and IMRB) may

be used to block a channel from making an interrupt

request. Writing a zero into the corresponding bit of

the mask register will still allow the channel to re-

ceive an interrupt and latch it into its pending bit (if

that channel is enabled), but will prevent that chan-

nel from making an interrupt request. If that channel

is causing an interrupt request at the time the cor-

responding bit in the mask register is cleared, the re-

quest will cease. If no other channel is making a re-

quest, INTR will go inactive. If the mask bit is re-en-

abled, any pending interrupt is now free to resume

its request unless blocked by a higher priority re-

quest for service. IMRA and IMRB are also readable

. A conceptual circuit of an interrupt channel is

shown in figure 10.

7/33