MAQ281C Просмотр технического описания (PDF) - Dynex Semiconductor

Номер в каталоге

Компоненты Описание

производитель

MAQ281C Datasheet PDF : 55 Pages

| |||

MAS281

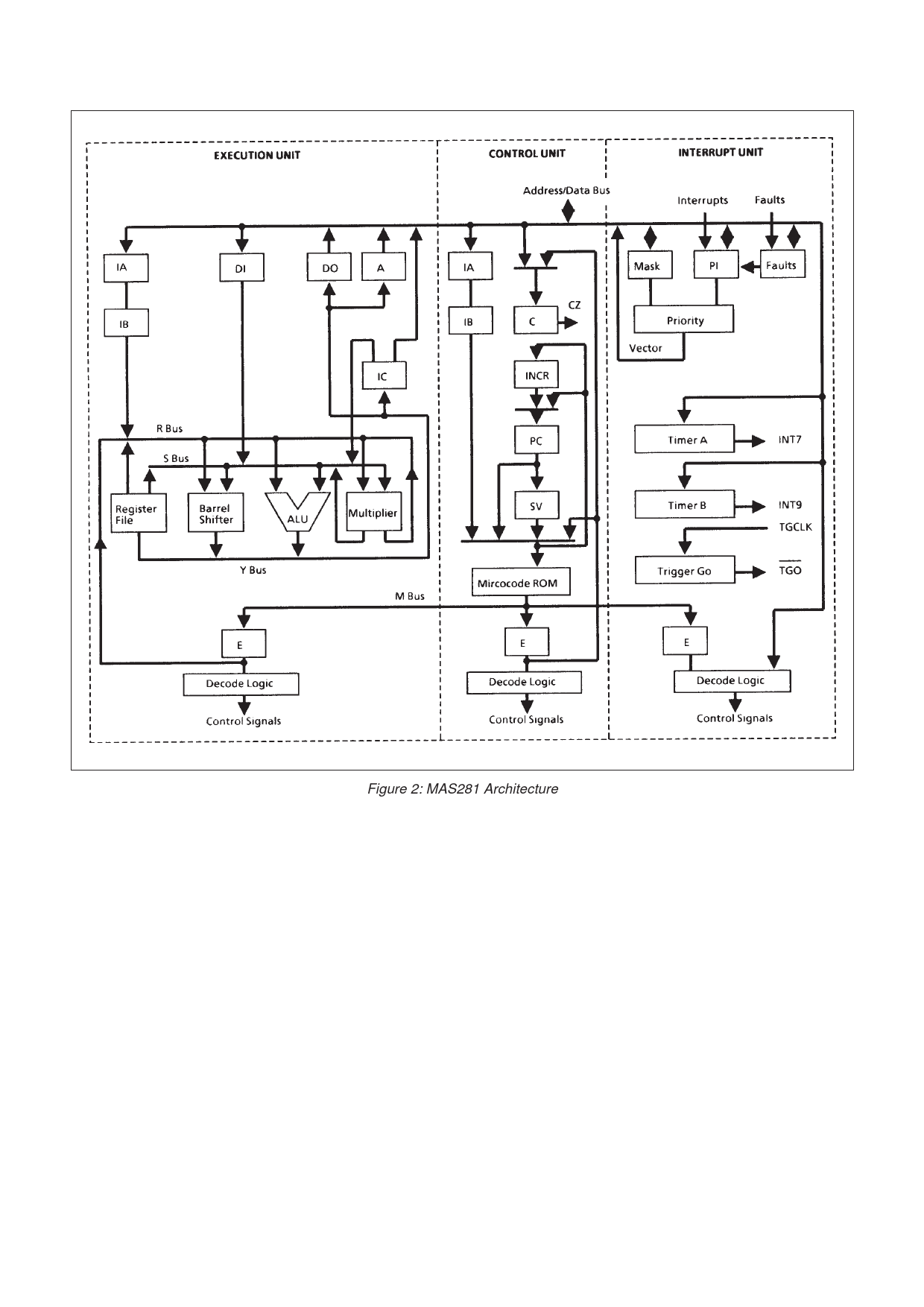

Figure 2: MAS281 Architecture

1.1.3 PARALLEL MULTIPLIER/ACCUMULATOR

This multiplies a 24-bit multiplicand by a 4-bit multiplier and

accumulates the product in a single machine cycle. Only four

iterations through the multiplier are required to complete a 16-

bit by 16-bit multiply.

1.1.4 BARREL SHIFTER

operations to determine which course of action to follow. The

AS field is used during expanded memory access to define the

page register set to be used for instruction and operand

memory references. The PS field is used during memory

protect operations to define the access key used for memory

accesses. The PS field is also used during execution of

privileged instructions. PS must be zero for such operations to

be legal. Figure 3 depicts the status register format

This shifter is a 32-bit input, 16-bit output right-shift

network. The barrel shifter allows multibit shifts to be

accomplished in a single machine cycle and is used by the

microcode for all shift, rotate, and normalise operations.

1.1.5 STATUS REGISTER

This 16-bit register holds the condition status (CS) bits C,

P, Z, and N; the 4-bit address state (AS) field; and the 4bit

processor state (PS) field. The CS bits are updated after each

logical, shift, and arithmetic operation performed by the ALU.

The CU interrogates these bits during conditional

1.1.6 STATE SEQUENCER

The EU utilises a state machine, clocked by the system

oscillator, to generate processor timing and control signals.

These signals constitute the lowest level of control available

within the module, and provide the framework for basic

operations, such as selecting the next microinstruction to be

executed, sequencing bus control signals to effect a memory

transfer, or performing an operation within the ALU. Each

complete pass through the state machine corresponds to one

such operation and constitutes a machine cycle.

3/55