DS2181A Просмотр технического описания (PDF) - Maxim Integrated

Номер в каталоге

Компоненты Описание

производитель

DS2181A Datasheet PDF : 32 Pages

| |||

DS2181A

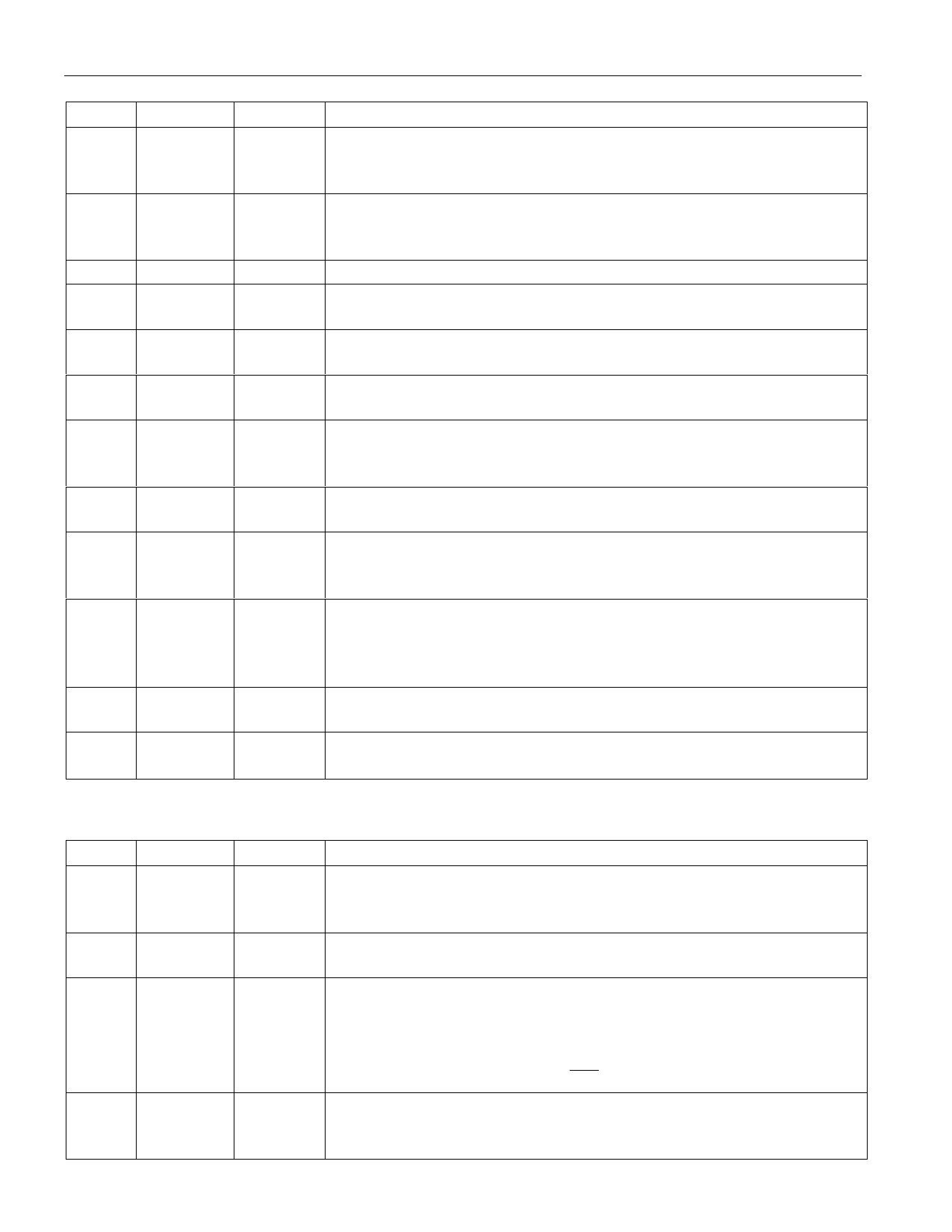

TRANSMIT PIN DESCRIPTION (40-PIN DIP ONLY) Table 1

PIN SYMBOL TYPE

DESCRIPTION

1 TMSYNC

I

Transmit Multiframe Sync. Low-high transition establishes start of

CAS and/or CRC4 multiframe. Can be tied low, allowing internal

multiframe counter to run free.

2 TFSYNC

I

Transmit Frame Sync. Low-high transition every frame period

establishes frame boundaries. Can be tied low, allowing TMSYNC to

establish frame boundaries.

3

TCLK

I

Transmit Clock. 2.048 MHz primary clock.

4 TCHCLK

O

Transmit Channel Clock. 256 kHz clock which identifies timeslot

boundaries. Useful for parallel-to-serial conversion of channel data.

5

TSER

I

Transmit Serial Data. NRZ data input, sampled on falling edges of

TCLK.

6

TMO

O Transmit Multiframe Out. Output of multiframe counter; high

during frame 0, low otherwise.

7

TXD

I

Transmit Extra Data. Sampled on falling edge of TCLK during bit

times 5, 7, and 8 of timeslot 16 in frame 0 when CAS signaling is

enabled.

8

TSTS

O Transmit Signaling Timeslot. High during timeslot 16 of every

frame, low otherwise.

9

TSD

I

Transmit Signaling Data. CAS signaling data input; sampled on

falling edges of TCLK for insertion into outgoing timeslot 16 when

enabled.

10

TIND

I

Transmit International and National Data. Sampled on falling

edge of TCLK during bit 1 time of timeslot 0 every frame

(international) and/or during bit times 4 through 8 of timeslot 0 during

non-align frames (national) when enabled.

11

TAF

O Transmit Alignment Frame. High during frames containing the

frame alignment signal, low otherwise.

12

TPOS

O Transmit Bipolar Data Outputs. Updated on rising edge of TCLK.

13

TNEG

SYCHRONIZER STATUS PIN (44-PIN PLCC ONLY) Table 2A

PIN SYMBOL TYPE

DESCRIPTION

3

RMSA

O Receive Multiframe Search Active. This pin will transition high

when the synchronizer searching for the CAS multiframe alignment

word is active.

6

RFSA

O Receive Frame Search Active. This pin will transition high when the

synchronizer searching for the FAS is active.

25

RCTO

O Receive CRC4 Time Out. This pin will transition high when the

RCTO counter reaches its maximum count of 32. The pin will return

low when either the DS2181AQ reaches CRC4 multiframe

synchronization, or if CRC4 is disabled via CRC.2, or if the device is

issued a hardware reset via the RST pin.

28

RCSA

O Receive CRC4 Search Active. This pin will transition high when the

synchronizer searching for the CRC4 multiframe alignment word is

active.

3 of 32