A80960JD Просмотр технического описания (PDF) - Unspecified

Номер в каталоге

Компоненты Описание

производитель

A80960JD Datasheet PDF : 59 Pages

| |||

PRODUCT PREVIEW

80960JD

3.3 V EMBEDDED 32-BIT MICROPROCESSOR

• 3.3 V, 5 V Tolerant, Version of the 80960JD Processor

s Pin/Code Compatible with all 80960Jx

s 3.3 V Supply Voltage

Processors

— 5 V Tolerant Inputs

s High-Performance Embedded Architecture

— TTL Compatible Outputs

— One Instruction/Clock Execution

s High Bandwidth Burst Bus

— Core Clock Rate is 2x the Bus Clock

— 32-Bit Multiplexed Address/Data

— Load/Store Programming Model

— Programmable Memory Configuration

— Sixteen 32-Bit Global Registers

— Selectable 8-, 16-, 32-Bit Bus Widths

— Sixteen 32-Bit Local Registers (8 sets)

— Supports Unaligned Accesses

— Nine Addressing Modes

— Big or Little Endian Byte Ordering

— User/Supervisor Protection Model

s High-Speed Interrupt Controller

s Two-Way Set Associative Instruction Cache — 31 Programmable Priorities

— 80960JD - 4 Kbyte

— Programmable Cache Locking

— Eight Maskable Pins plus NMI

— Up to 240 Vectors in Expanded Mode

Mechanism

s Two On-Chip Timers

s Direct Mapped Data Cache

— Independent 32-Bit Counting

— 80960JD - 2 Kbyte

— Write Through Operation

— Clock Prescaling by 1, 2, 4 or 8

— lnternal Interrupt Sources

s On-Chip Stack Frame Cache

— Seven Register Sets Can Be Saved

— Automatic Allocation on Call/Return

— 0-7 Frames Reserved for High-Priority

Interrupts

s On-Chip Data RAM

— 1 Kbyte Critical Variable Storage

— Single-Cycle Access

s Halt Mode for Low Power

s IEEE 1149.1 (JTAG) Boundary Scan

Compatibility

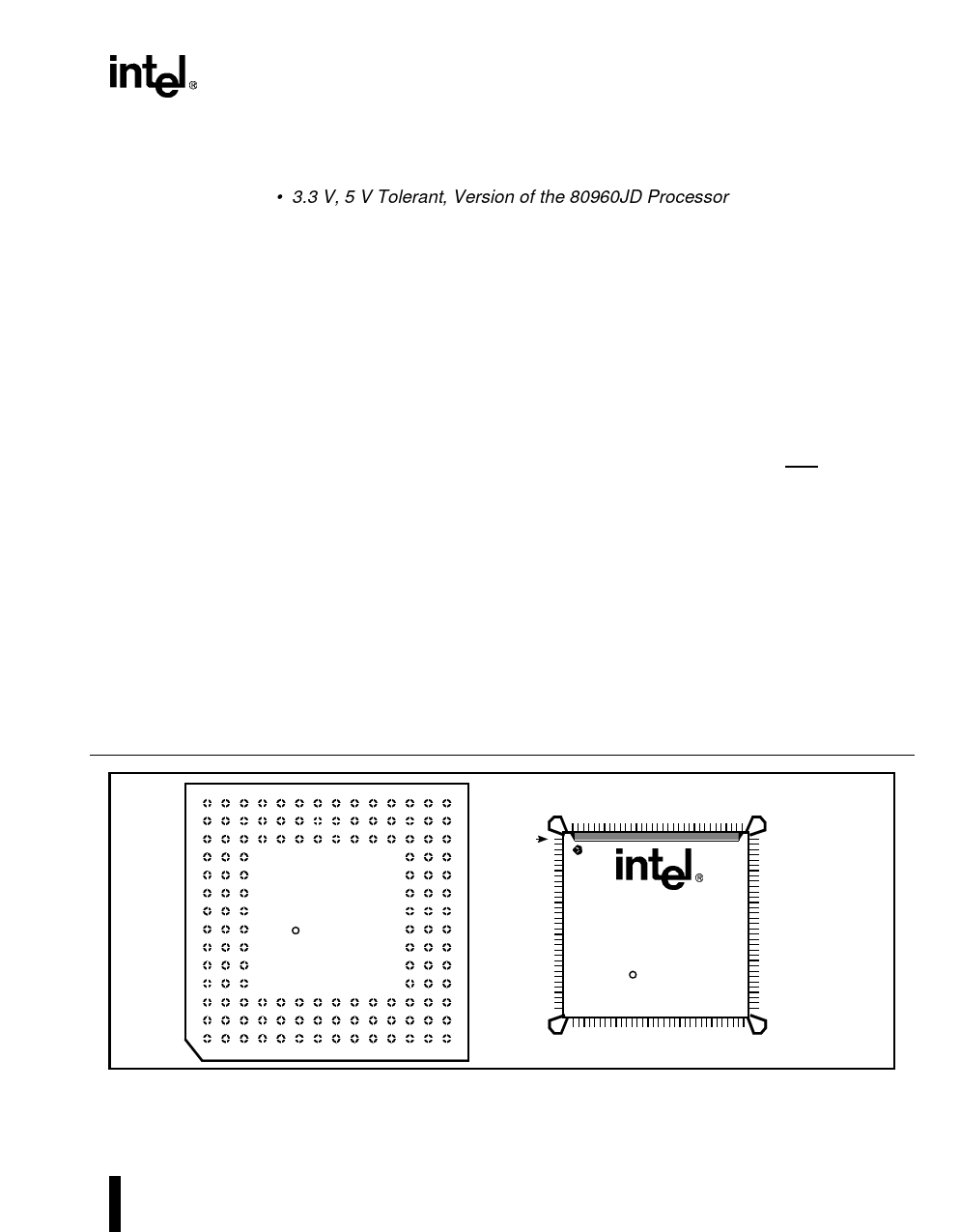

s Packages

— 132-Lead Pin Grid Array (PGA)

— 132-Lead Plastic Quad Flat Pack (PQFP)

132

PIN 1

99

iA80960JD

XXXXXXXXC0

M © 19xx

i960®

iNG80960JD

XXXXXXXXC0S

M © 19xx

33

66

Figure 1. 80960JD Microprocessor

© INTEL CORPORATION, 1996

November 1996

Order Number: 272971-001