SI531 Просмотр технического описания (PDF) - Silicon Laboratories

Номер в каталоге

Компоненты Описание

производитель

SI531 Datasheet PDF : 10 Pages

| |||

Si530/531

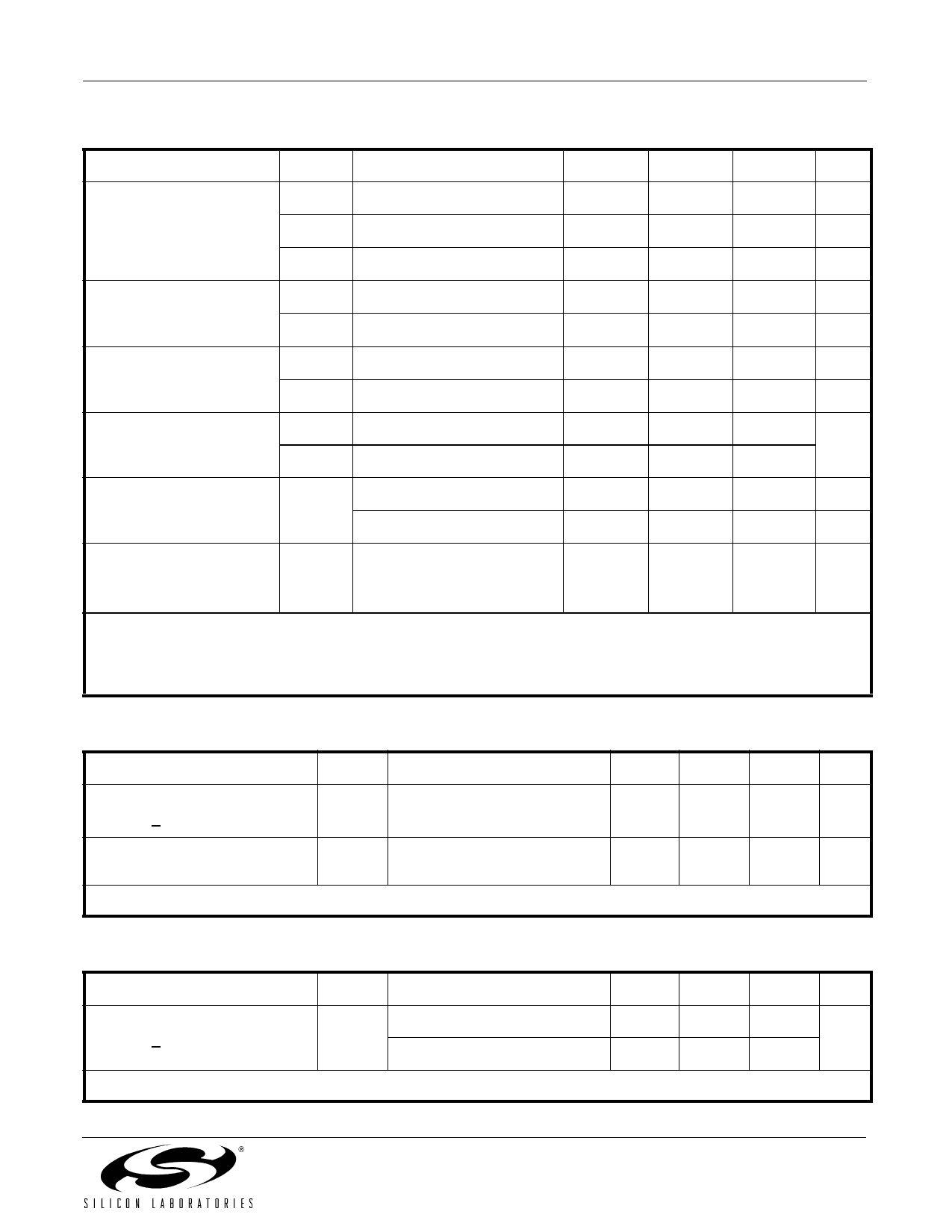

Table 3. CLK± Output Levels and Symmetry

Parameter

LVPECL Output Option1

LVDS Output Option2

CML Output Option2

CMOS Output Option3

Rise/Fall time (20/80%)

Symbol

VO

VOD

VSE

VO

VOD

VO

VOD

VOH

VOL

tR, tF

Test Condition

mid-level

swing (diff)

swing (single-ended)

mid-level

swing (diff)

mid-level

swing (diff)

IOH = 32 mA

IOL = 32 mA

LVPECL/LVDS/CML

CMOS with CL = 15 pF

Min

Typ

Max Units

VDD – 1.42

1.1

0.5

1.125

—

—

—

1.20

VDD – 1.25 V

1.9

VPP

0.93

VPP

1.275

V

0.32

0.40

0.50

VPP

—

VDD – 0.75

—

V

0.70

0.95

1.20

VPP

0.8 x VDD

—

—

—

VDD

V

0.4

—

—

350

ps

—

1

—

ns

Symmetry (duty cycle)

SYM LVPECL: VDD – 1.3 V (diff)

LVDS: 1.25 V (diff)

45

—

55

%

CMOS: VDD/2

Notes:

1. 50 Ω to VDD – 2.0 V.

2. Rterm = 100 Ω (differential).

3. CL = 15 pF

Table 4. CLK± Output Phase Jitter

Parameter

Symbol

Test Condition

Min

Phase Jitter (RMS)*

for FOUT > 500 MHz

φJ

12 kHz to 20 MHz (OC-48)

—

50 kHz to 80 MHz (OC-192)

—

Phase Jitter (RMS)*

for FOUT of 125 to 500 MHz

φJ

12 kHz to 20 MHz (OC-48)

—

*Note: Differential Modes: LVPECL/LVDS/CML. Refer to AN256 for further information.

Typ

0.27

0.30

0.50

Max Units

—

ps

—

—

ps

Table 5. CLK± Output Period Jitter

Parameter

Symbol

Test Condition

Min

Typ

Max Units

Period Jitter*

for FOUT < 160 MHz

JPER

RMS

Peak-to-Peak

—

1

—

ps

—

5

—

*Note: Any output mode, including CMOS, LVPECL, LVDS, CML. N = 1000 cycles.

Preliminary Rev. 0.4

3