CDB8952 Просмотр технического описания (PDF) - Cirrus Logic

Номер в каталоге

Компоненты Описание

производитель

CDB8952 Datasheet PDF : 86 Pages

| |||

CS8952T

CrystalLAN™ 100BASE-X and 10BASE-T Transceiver

If either BPALIGN or BP4B5B is asserted, then this pin is re-defined as RXD4 (Receive

Data 4), the most-significant bit of the received five-bit code-group. If the 4B5B encoder is

being bypassed, receive data is present when RX_DV is asserted. If alignment is being

bypassed, data reception is continuous.

At power-up or at reset, the logic value on this pin is latched into bit 4 of the PHY Address

field of the Self Status Register (address 19h). This pin includes a weak internal pull-down

(> 20 KΩ), or the value may be set by an external 4.7 KΩ pull-up or pull-down resistor.

In order to conform with Annex 22B of the IEEE 802.3u specification, the MII_DRV pin

should be pulled high during power-up or reset, and the RX_ER pin should have an external

33 Ω series resistor. For systems not required to drive external connectors and cables as

described in the IEEE802.3u specification, the external series resistor may not be necessary.

RXD3/PHYAD3 - Receive Data 3/PHY Address 3. Input/Tri-State Output, Pin 29.

RXD2 - Receive Data 2. Tri-State Output, Pin 30.

RXD1/PHYAD1 - Receive Data 1/PHY Address 1. Input/Tri-State Output, Pin 31.

RXD0 - Receive Data 0. Tri-State Output, Pin 32.

Receive data output. Receive data is present when RX_DV is asserted. RXD0 is the least-

significant bit. For MII modes, nibble-wide data (synchronous to RX_CLK) is transferred on

pins RXD[3:0]. In 10 Mb/s serial mode, pin RXD0 is used as the serial output pin, and

RXD[3:1] are ignored. When either BP4B5B or BPALIGN is selected, pin RXD4 contains the

most-significant bit of the five-bit code-group.

At power-up or at reset, the value on RXD1/PHYAD1 is latched into bit 1 of the PHY Address

field of the Self Status Register (address 19h). This pin includes a weak internal pull-down

(> 20 KΩ), or the value may be set by an external 4.7 KΩ pull-up or pull-down resistor.

At power-up or at reset, the logic value on RXD3/PHYAD3 is latched into bit 3 of the PHY

Address field of the Self Status Register (address 19h). This pin includes a weak internal pull-

down (> 20 KΩ), or the value may be set by an external 4.7 KΩ pull-up or pull-down resistor.

In order to conform with Annex 22B of the IEEE 802.3u specification, the MII_DRV pin

should be pulled high during power-up or reset, and the RXD[3:0] pins should have external

33 Ω series resistors. For systems not required to drive external connectors and cables as

described in the IEEE802.3u specification, the external series resistors may not be necessary.

TX_CLK - Transmit Clock. Input/Tri-State Output, Pin 42.

Continuous clock signal used by the CS8952T as a reference clock to sample TXD[3:0],

TX_ER, and TX_EN. TX_CLK can be referenced either internally (Output Mode) or externally

(Input Mode) based upon the value of the TCM pin at power-up or at reset.

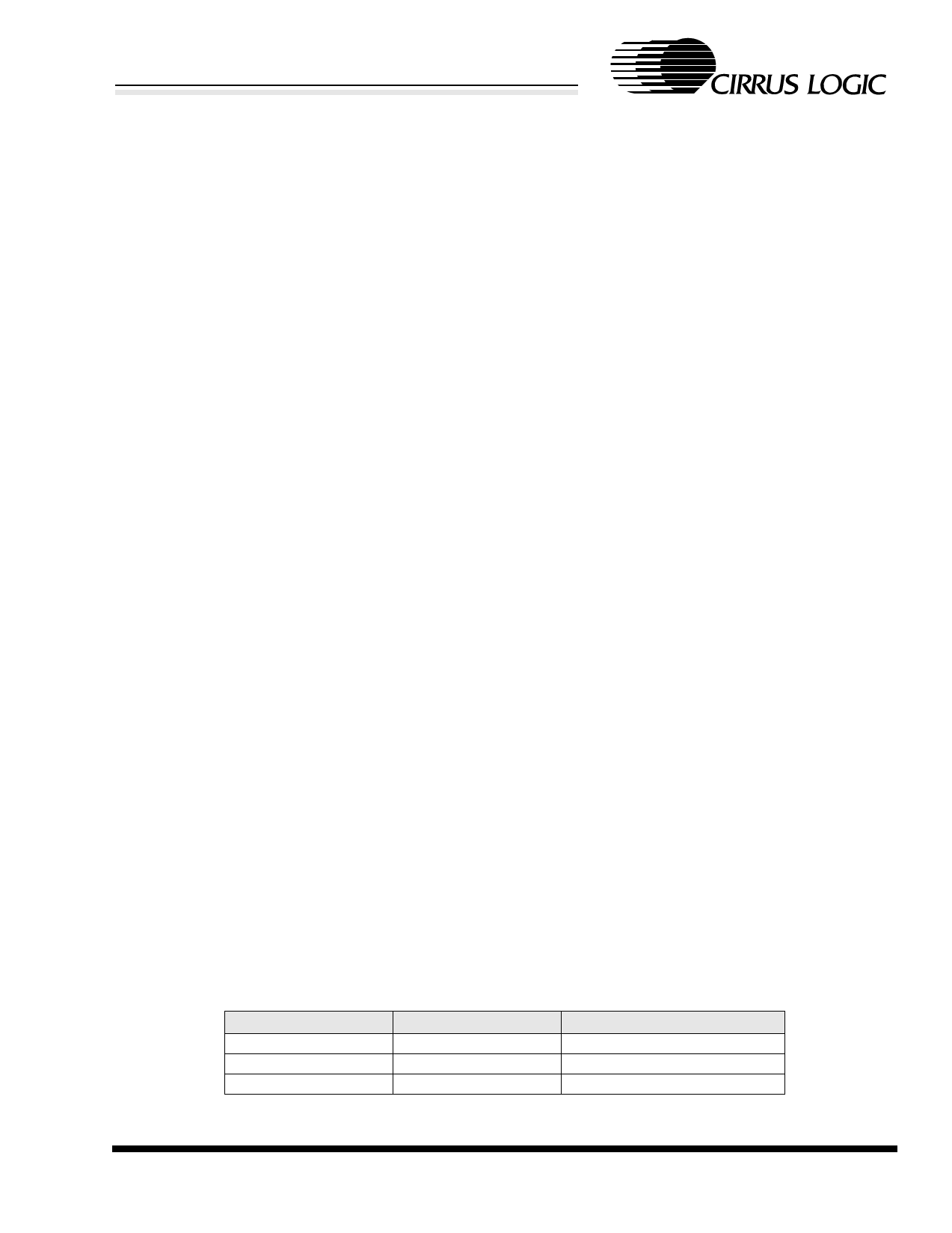

TCM pin

high

floating

low

TX_CLK mode

TX_CLK is input

TX_CLK is input

TX_CLK is output

CLK25 status

CLK25 pin is an output

CLK25 is disabled

CLK25 is disabled

CIRRUS LOGIC ADVANCED PRODUCT DATABOOK

DS206TPP2

9