AS5SS256K18DQ-9/XT Просмотр технического описания (PDF) - Micross Components

Номер в каталоге

Компоненты Описание

производитель

AS5SS256K18DQ-9/XT Datasheet PDF : 14 Pages

| |||

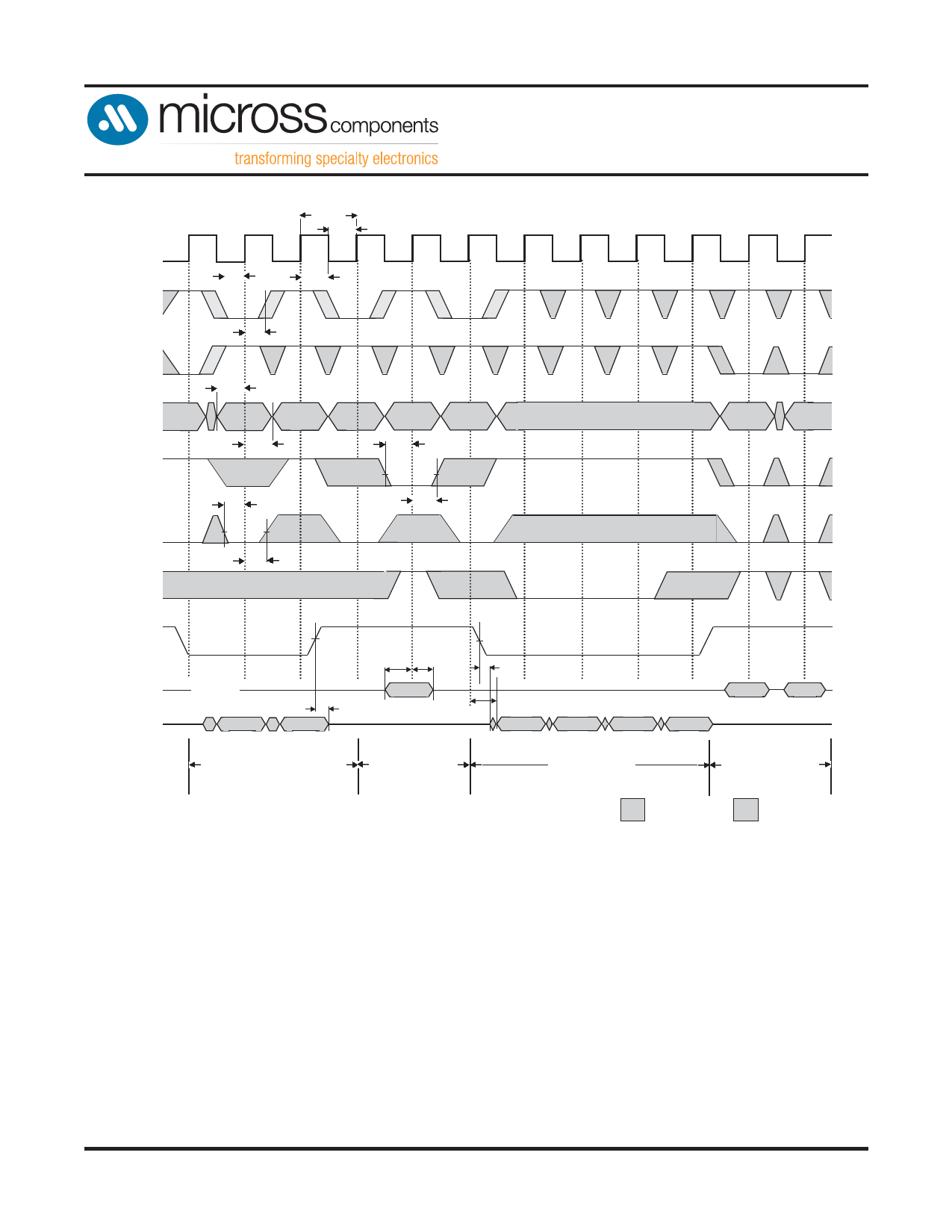

CLK

tADSS

ADSP\

ADSC\

ADDRESS A1

BWE\, GW\

BWa\ - BWb\

CE\

(Note 2)

ADV\

tADSH

tAS

A2

tAH

tCES

tCEH

tKC READ/WRITE TIMING6

tKL

tKH

A3

A4

tWS

tWH

SSRAM

AS5SS256K18

A5 A6

OE\

tDS tDH

D

High-Z

tOEHZ

Q

Q(A1) Q(A2)

D(A3)

t

OELZ

t

KQ

Q(A4)

(NOTE 1)

Q(A4+1) Q(A4+2)

Q(A4+3)

D(A5)

D(A6)

Back-to-Back READS

(NOTE 5)

SINGLE WRITE

BURST READ

Back-to-Back

WRITE’s

Don’t Care

Undefined

NOTE: 1. Q(A4) refers to output from address A4. Q(A4+1) refers to output from the next internal burst address following A4.

2. CE2\ and CE2 have timing identical to CE\. On this diagram, when CE\ is LOW, CE2\ is LOW and CE2 is HIGH. When CE\ is HIGH, CE2\ is HIGH and CE2 is LOW.

3. The data bus (Q) remains in High-Z following a WRITE cycle unless an ADSP\, ADSC\, or ADV\ cycle is performed.

4. GW\ is HIGH.

5. Back-to-back READs may be controlled by either ADSP\ or ADSC\.

6. Timing is shown assuming that the device was not enabled before entering into this sequence.

AS5SS256K18

Rev. 2.5 10/13

11

Micross Components reserves the right to change products or specifications without notice.