M4A5-384/128-5SAC –ü—Ä–ĺ—Ā–ľ–ĺ—ā—Ä —ā–Ķ—Ö–Ĺ–ł—á–Ķ—Ā–ļ–ĺ–≥–ĺ –ĺ–Ņ–ł—Ā–į–Ĺ–ł—Ź (PDF) - Lattice Semiconductor

–Ě–ĺ–ľ–Ķ—Ä –≤ –ļ–į—ā–į–Ľ–ĺ–≥–Ķ

–ö–ĺ–ľ–Ņ–ĺ–Ĺ–Ķ–Ĺ—ā—č –ě–Ņ–ł—Ā–į–Ĺ–ł–Ķ

–Ņ—Ä–ĺ–ł–∑–≤–ĺ–ī–ł—ā–Ķ–Ľ—Ć

M4A5-384/128-5SAC

M4A5-384/128-5SAC Datasheet PDF : 63 Pages

| |||

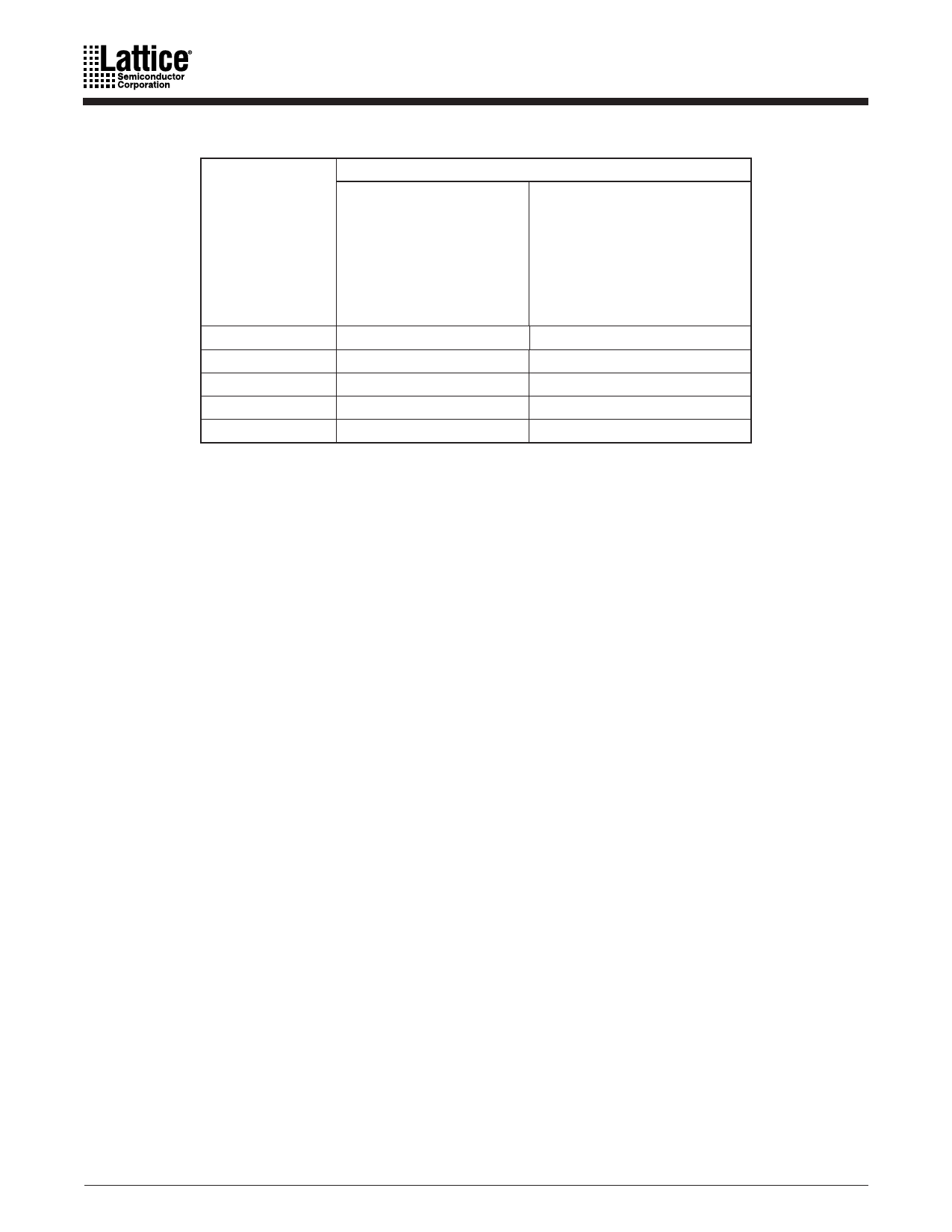

Table 4. Architectural Summary of ispMACH 4A devices

Macrocell-I/O Cell Ratio

Input Switch Matrix

Input Registers

Central Switch Matrix

Output Switch Matrix

ispMACH 4A Devices

M4A3-64/32, M4A5-64/32

M4A3-96/48, M4A5-96/48

M4A3-128/64, M4A5-128/64

M4A3-192/96, M4A5-192/96

M4A3-256/128, M4A5-256/128

M4A3-384

M4A3-512

M4A3-32/32

M4A5-32/32

M4A3-64/64

M4A3-256/160

M4A3-256/192

2:1

1:1

Yes

Yes1

Yes

No

Yes

Yes

Yes

Yes

The Macrocell-I/O cell ratio is defined as the number of macrocells versus the number of I/O cells

internally in a PAL block (Table 4).

The central switch matrix takes all dedicated inputs and signals from the input switch matrices and routes

them as needed to the PAL blocks. Feedback signals that return to the same PAL block still must go through

the central switch matrix. This mechanism ensures that PAL blocks in ispMACH 4A devices communicate

with each other with consistent, predictable delays.

The central switch matrix makes a ispMACH 4A device more advanced than simply several PAL devices on

a single chip. It allows the designer to think of the device not as a collection of blocks, but as a single

programmable device; the software partitions the design into PAL blocks through the central switch matrix

so that the designer does not have to be concerned with the internal architecture of the device.

Each PAL block consists of:

‚óÜ Product-term array

‚óÜ Logic allocator

‚óÜ Macrocells

‚óÜ Output switch matrix

‚óÜ I/O cells

‚óÜ Input switch matrix

‚óÜ Clock generator

Notes:

1. M4A3-64/64 internal switch matrix functionality embedded in central switch matrix.

6

ispMACH 4A Family