A14100 Просмотр технического описания (PDF) - Actel Corporation

Номер в каталоге

Компоненты Описание

производитель

A14100 Datasheet PDF : 68 Pages

| |||

Accelerator Series FPGAs – ACT™ 3 Family

D

ODE

0

MUX

1

DQ

CLR/PRE

0

MUX

1

DATAOUT

S0 0

S1

1

Y

MUX 2

1

3

QD

MUX

0

CLR/PRE

DATAIN

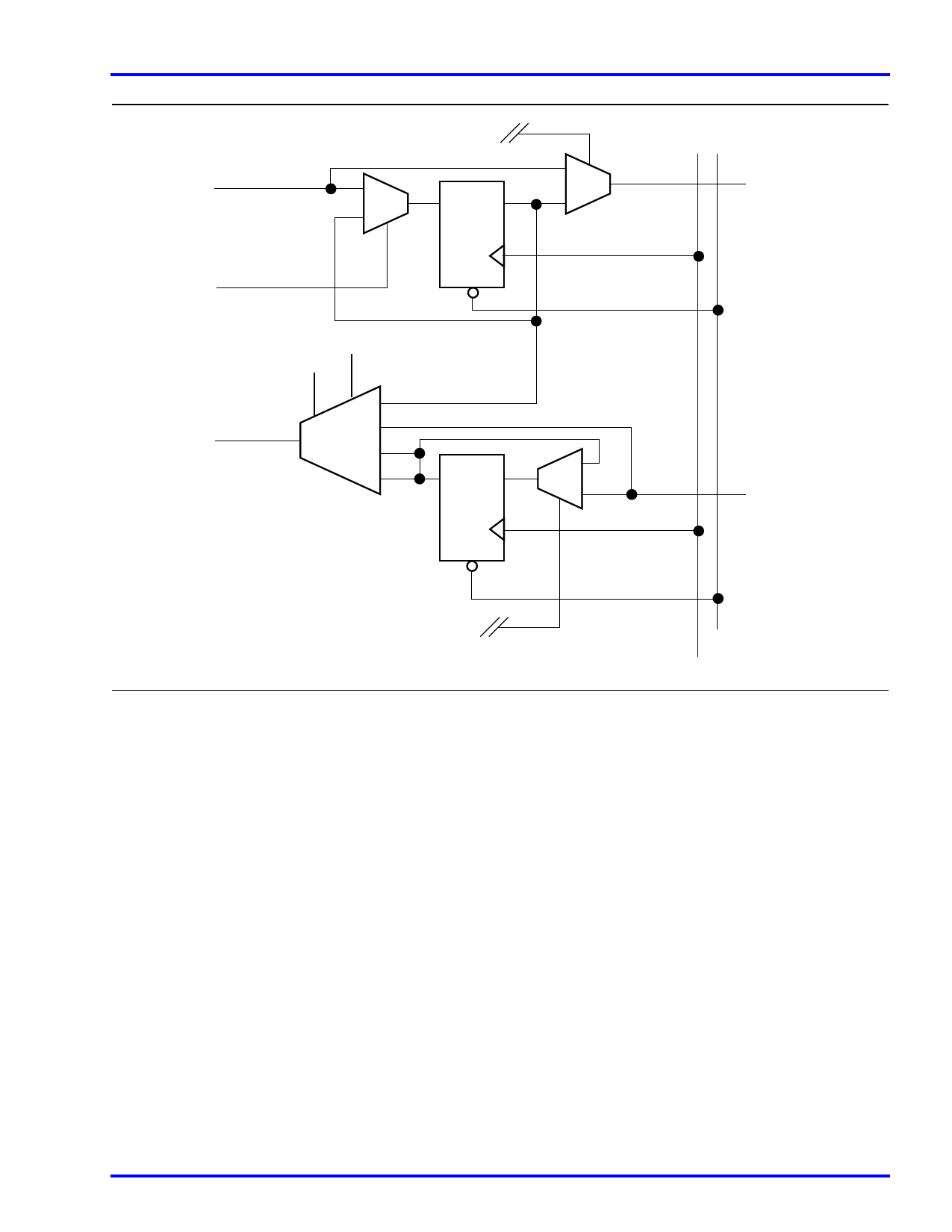

Figure 4 • Functional Diagram for I/O Module

I/O Pad Drivers

All pad drivers are capable of being tristate. Each buffer

connects to an associated I/O module with four signals: OE

(Output Enable), IE (Input Enable), DataOut, and DataIn.

Certain special signals used only during programming and

test also connect to the pad drivers: OUTEN (global output

enable), INEN (global input enable), and SLEW (individual

slew selection). See Figure 5.

Special I/Os

The special I/Os are of two types: temporary and permanent.

Temporary special I/Os are used during programming and

testing. They function as normal I/Os when the MODE pin is

inactive. Permanent special I/Os are user programmed as

either normal I/Os or special I/Os. Their function does not

change once the device has been programmed. The

permanent special I/Os consist of the array clock input

buffers (CLKA and CLKB), the hard-wired array clock input

buffer (HCLK), the hard-wired I/O clock input buffer

(IOCLK), and the hard-wired I/O register preset/clear input

IOPCL

IOCLK

buffer (IOPCL). Their function is determined by the I/O

macros selected.

Clock Networks

The ACT 3 architecture contains four clock networks: two

high-performance dedicated clock networks and two general

purpose routed networks. The high-performance networks

function up to 200 MHz, while the general purpose routed

networks function up to 150 MHz.

Dedicated Clocks

Dedicated clock networks support high performance by

providing sub-nanosecond skew and guaranteed

performance. Dedicated clock networks contain no

programming elements in the path from the I/O Pad Driver to

the input of S-modules or I/O modules. There are two

dedicated clock networks: one for the array registers (HCLK),

and one for the I/O registers (IOCLK). The clock networks

are accessed by special I/Os.

1-183