THC63LVD104C Просмотр технического описания (PDF) - THine Electronics, Inc.

Номер в каталоге

Компоненты Описание

производитель

THC63LVD104C Datasheet PDF : 13 Pages

| |||

THC63LVD104C_Rev.2.1_E

THC63LVD104C

112MHz 30Bits COLOR LVDS Receiver

General Description

The THC63LVD104C receiver is designed to support

pixel data transmission between Host and Flat Panel

Display from NTSC up to SXGA resolutions. The

THC63LVD104C converts the LVDS data streams back

into 35bits of CMOS/TTL data with the choice of the

rising edge or falling edge clock for the convenience

with a variety of LCD panel controllers.At a transmit

clock frequency of 112MHz, 30bits of RGB data and

5bits of timing and control data (HSYNC,

VSYNC,DE,CNTL1,CNTL2) are transmitted at an

effective rate of 784Mbps per LVDS channel.Using a

112MHz clock, the data throughput is 490Mbytes per

second.

Features

• Wide dot clock range: 8-112MHz suited for NTSC,

VGA, SVGA, XGA, and SXGA

• PLL requires no external components

• 50% output clock duty cycle

• TTL clock edge programmable

• Power down mode

• Low power single 3.3V CMOS design

• 64pin TQFP

• Backward compatible with THC63LVDF64x

(18bits) / F84x(24bits)

• Pin compatible with THC63LVD104A

• Fail-safe for Open LVDS Input

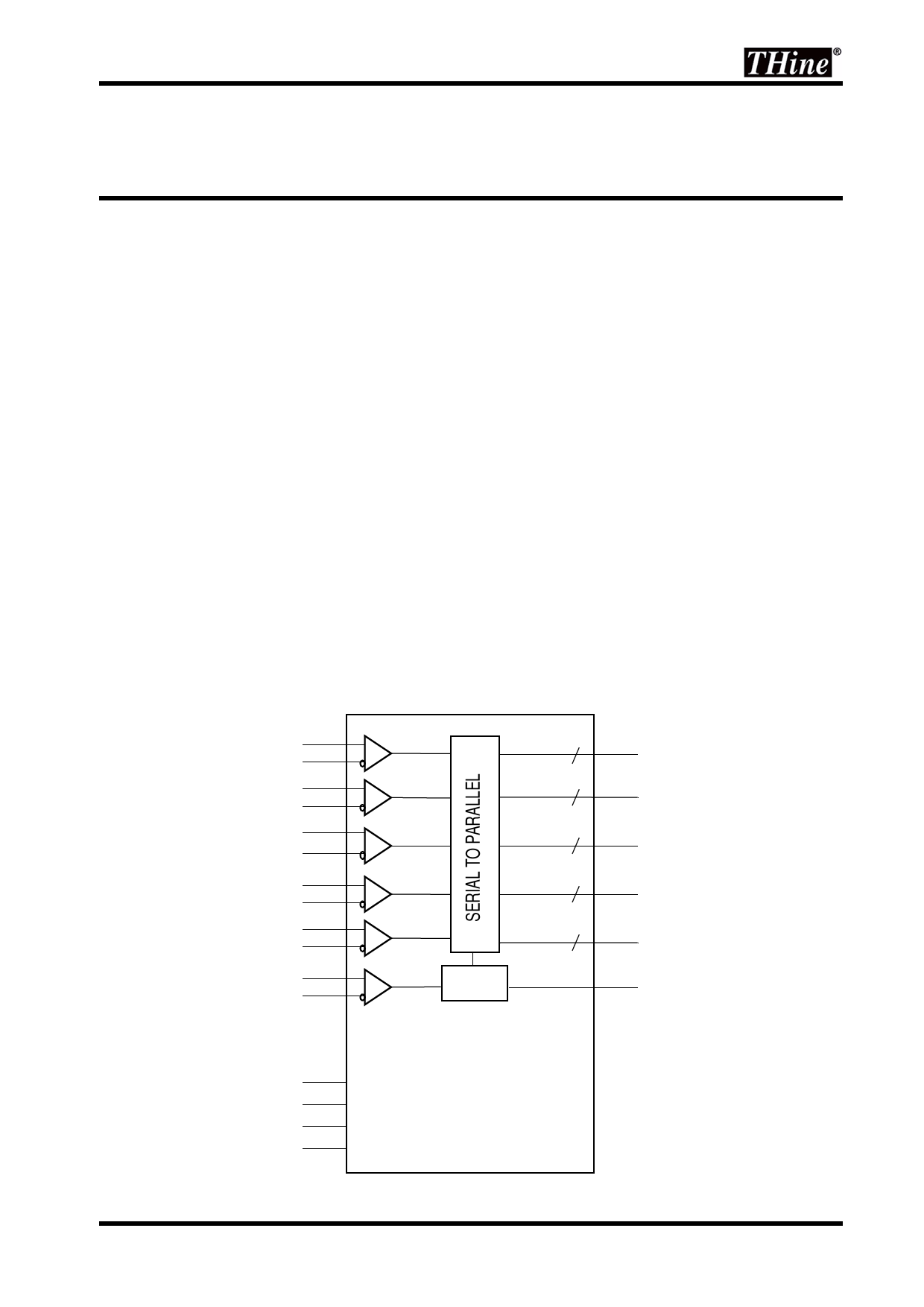

Block Diagram

LVDS INPUT

RA+/-

RB+/-

RC+/-

RD+/-

RE+/-

RCLK+/-

(8 to 112MHz)

CMOS/TTL INPUT

TEST

PD

OE

R/F

Copyright©2010 THine Electronics, Inc.

CMOS/TTL OUTPUT

7

RA6-RA0

7

RB6-RB0

7

RC6-RC0

7

RD6-RD0

7

RE6-RE0

PLL

CLKOUT

1/13

THine Electronics, Inc.