KE5BCCA9M Просмотр технического описания (PDF) - KAWASAKI MICROELECTRONICS

Номер в каталоге

Компоненты Описание

производитель

KE5BCCA9M Datasheet PDF : 19 Pages

| |||

Kawasaki LSI

9M Classification CAM

PRELIMINARY

3. Pin Descriptions

3.1. Pin Assignment (T.B.D.)

Pin assignment is backward compatible with 4.7M CAM (KE5BCCA4M). OD[23] is assigned to the

NC pin of 4.7M CAM, and CNTL[15:14] to the GND pins.

VDDQ (I/O): 2.5V or 1.8V --- Selectable I/O voltage (T.B.D.)

VDD (core): 1.2V

3.2. Pin Descriptions

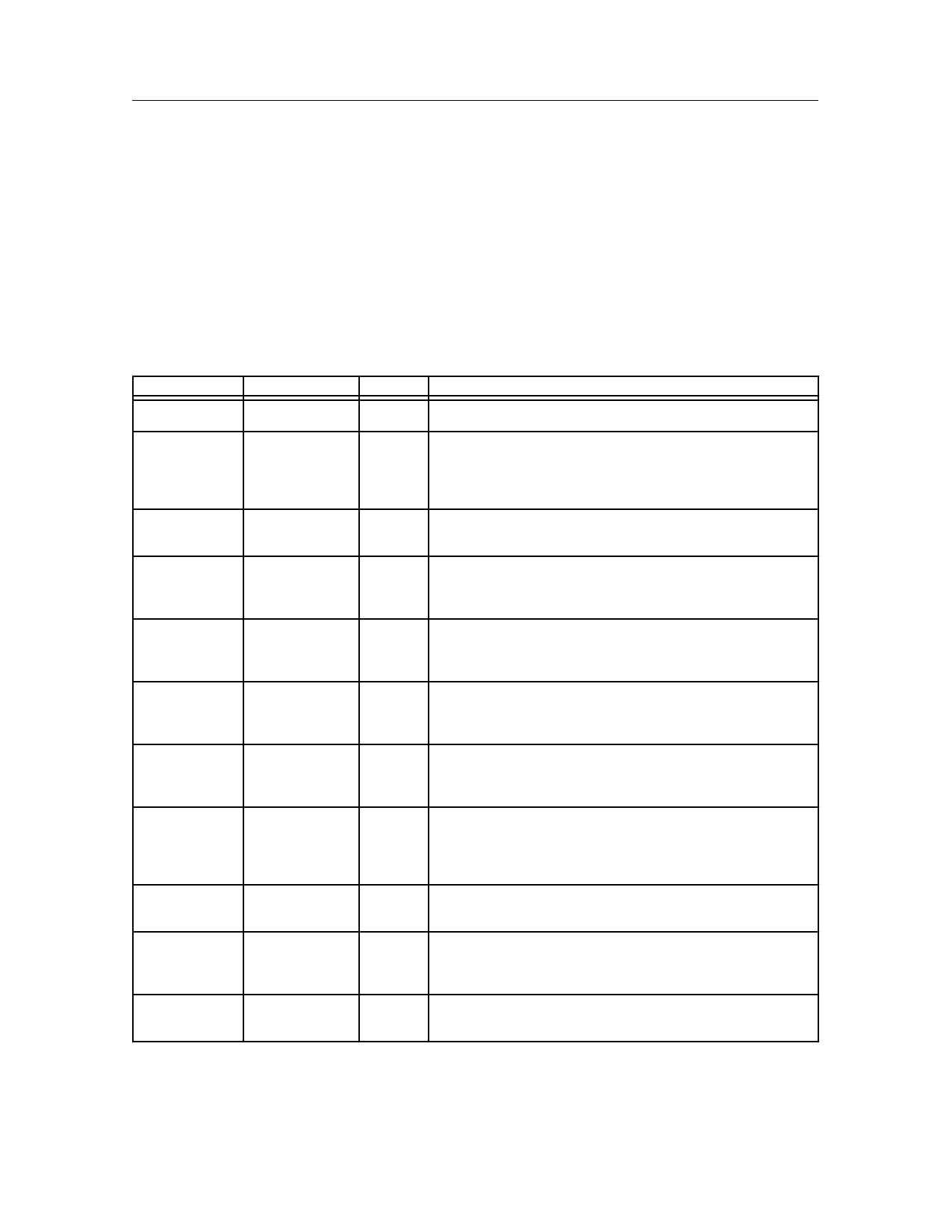

Pin Name

RSTN

CLK

INPMD

DAT[63:0]

EDAT[7:0]

DATWDT

CNTL[15:0]

SAD

CEN

RWN

OEDATN

Description

Attribute Function

Hardware Reset Input

RSTN low resets the device.

Clock

Input

CLK is the clock input. All operations are synchronized with CLK.

The internal PLL generate the double rate clock of CLK, called

CLKX2 and all input signals are referenced to the CLKX2.

Input Mode

Input

I/O Port

Data Bus

Input/

Output

Tristate

EXTRA Bit Data

Bus

Input/

Output

Tristate

I/O Port Data Bus Input

Width

Control Bus

Input

Sub Address

Input

Device Enable Input

Read/Write

Input

I/O Port Data Bus Input

Output Enable

When all input signals are referenced to only CLK rising edge;

not falling edge, fix INPMD high.

DAT[63:0] is a 64-bit bi-directional data bus for read/write of

CAM memory and registers. RWN controls the bus direction.

EDAT[7:0] is a 8-bit bi-directional data bus for read/write of

EXTRA bits of CAM memory and registers. RWN controls the

bus direction.

DATWDT defines DAT[63:0] width. Fix low to employ all

DAT[63:0]; fix high not to employ DAT[63:32] and to employ

DAT[31:0] with SAD as a substitute for DAT[63:0].

CNTL[15:0] is the 16-bit control bus to control the device. The

search operations, the command assertions, and the register

accesses are invoked corresponding to CNTL[15:0].

SAD assigns DAT[31:0] to internal 64-bit data bus when

DAT[63:32] is unused (DATWDT=high). When SAD is low,

DAT[31:0] is assigned to lower 32-bit; when high, it is assigned

to upper 32-bit.

CEN low invokes operations such as read/write, search and

command.

RWN determines the direction of the I/O Port data bus

DAT[63:0] and that of the EXTRA bit data bus EDAT[7:0]. RWN

low selects a write cycle and RWN high selects a read cycle.

OEDATN is output enable signal for DAT[63:0] and EDAT[7:0].

This signal is also referenced to CLK rising edge.

Version 1.2.0

4

Confidential