ML7041 Просмотр технического описания (PDF) - Unspecified

Номер в каталоге

Компоненты Описание

производитель

ML7041 Datasheet PDF : 28 Pages

| |||

FEDL7041-05

ML7041

SDA, SCL

SDA is the serial data input/output pin and SCL is the serial clock line input pin. A pull-up register of 1 to 10 k is

required for the SDA pin. The master clock is required when data is written or read.

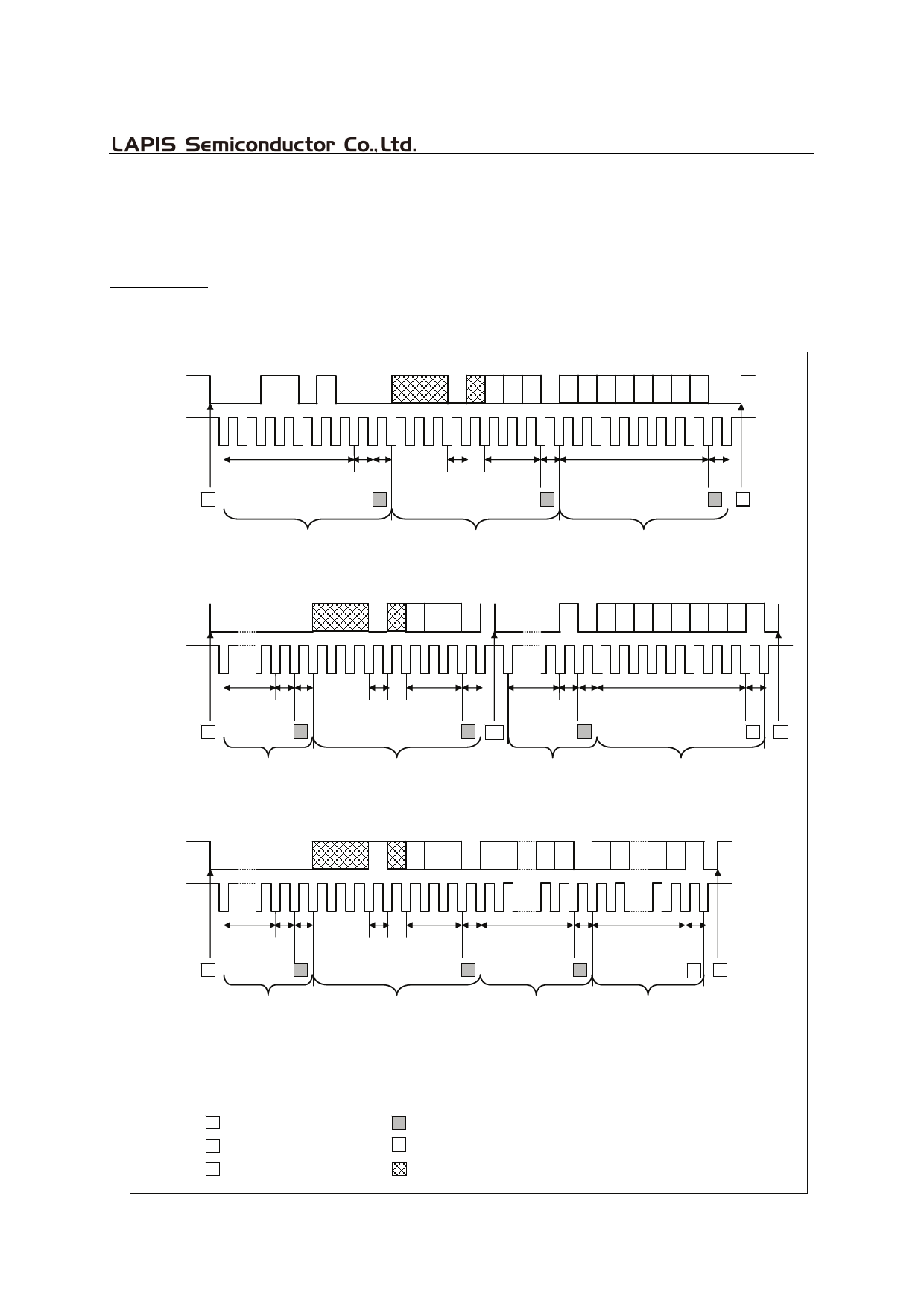

Transfer format

The control register can be controlled according to the I2C bus transfer format.

The control register address is 3 bits long and the register data is 8 bits long. The methods of writing and

reading of data are shown below.

SDA

SCL

A2 A1 A0 B7 B6 B5 B4 B3 B2 B1 B0

S

7-bit slave address

“0011010”

R/W

“0” A

read-back

mode bit

“0”

register

address

A

register data

AP

slave address write

register address write

register data write

Figure 3 I2C Interface Write Timing

SDA

SCL

A2 A1 A0

B7 B6 B5 B4 B3 B2 B1 B0

slave

address

R/W

“0”

S

A

read-back

mode bit

“0”

register

address

A

slave

address

R/W

“1”

Sr

A

register data

AP

slave address write

register address write

slave address write

register data read

Figure 4 I2C Interface Read Timing: normal mode

SDA

SCL

A2 A1 A0 B7 B6 B1 B0 B7 B6 B1 B0

slave

address

R/W

“0”

S

A

read-back

mode bit

“1”

register

address

A

register data

A

register data

AP

slave address write register address write

register data write register data read

Figure 5 I2C Interface Read Timing: read-back mode

ML7041 Slave address “0011010”

S START condition

P STOP condition

A Acknowledged (ML7041 drive SDA to “0”)

A Not Acknowledged

Sr Repeated START condition

Don’t care (“0” or “1”)

9/28