ACT8931AQJ633-T Просмотр технического описания (PDF) - Active-Semi, Inc

Номер в каталоге

Компоненты Описание

производитель

ACT8931AQJ633-T Datasheet PDF : 43 Pages

| |||

ACT8931A

Rev 3, 29-Nov-12

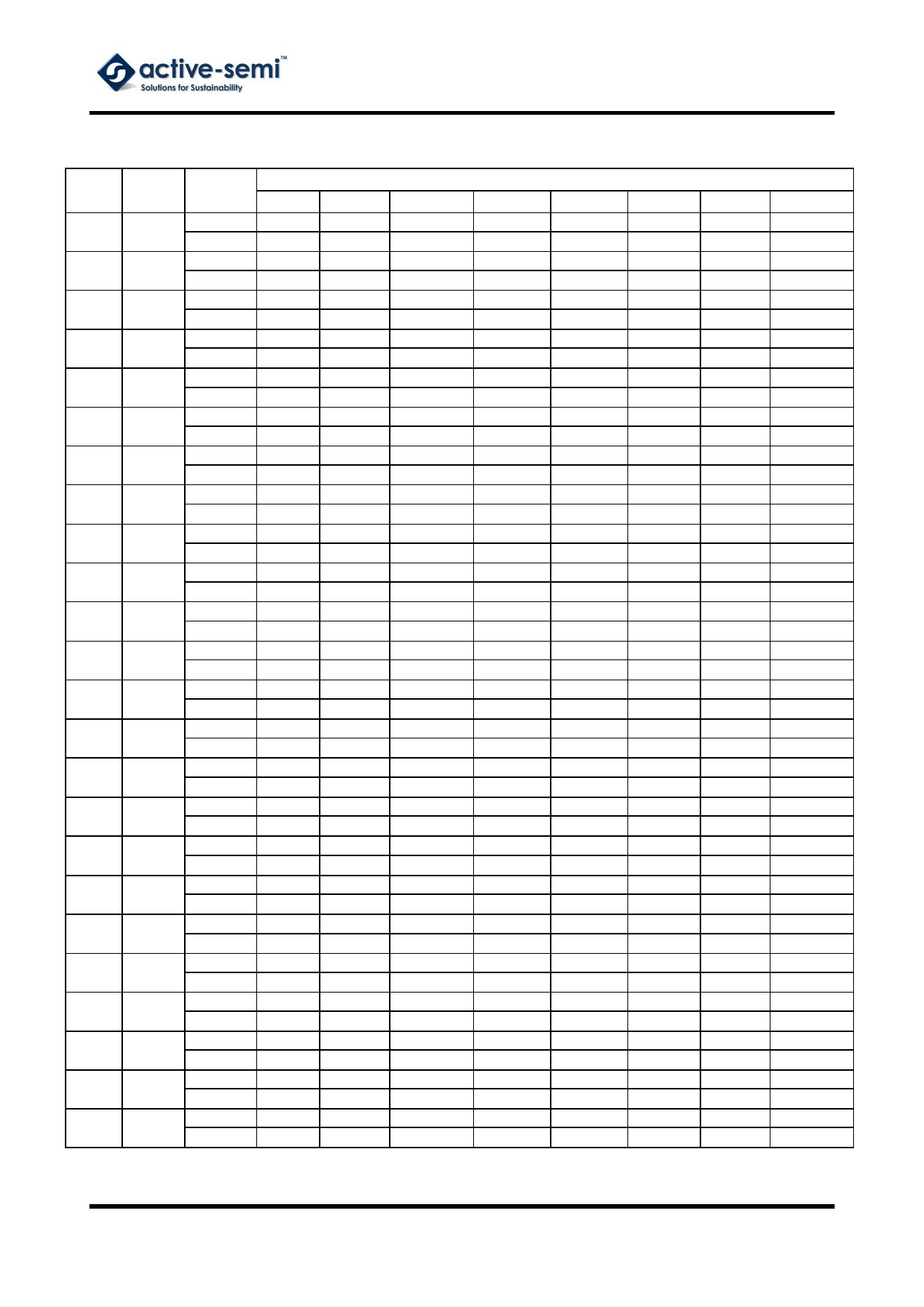

GLOBAL REGISTER MAP

OUTPUT ADDRESS

D7

D6

D5

BITS

D4

D3

D2

D1

D0

SYS

SYS

REG1

REG1

REG1

REG2

REG2

REG2

REG3

REG3

REG3

REG4

REG4

REG5

REG5

REG6

REG6

REG7

REG7

APCH

APCH

APCH

APCH

APCH

0x00

0x01

0x20

0x21

0x22

0x30

0x31

0x32

0x40

0x41

0x42

0x50

0x51

0x54

0x55

0x60

0x61

0x64

0x65

0x70

0x71

0x78

0x79

0x7A

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

NAME

DEFAULT

TRST nSYSMODE nSYSLEVMSK nSYSSTAT SYSLEV[3] SYSLEV[2] SYSLEV[1] SYSLEV[0]

0

1

0

R

0

1

1

1

Reserved Reserved MSTROFF Reserved SCRATCH SCRATCH SCRATCH SCRATCH

0

0

0

0

0

0

0

0

Reserved Reserved VSET1[5] VSET1[4] VSET1[3] VSET1[2] VSET1[1] VSET1[0]

0

0

1

1

1

0

0

1

Reserved Reserved VSET2[5] VSET2[4] VSET2[3] VSET2[2] VSET2[1] VSET2[0]

0

0

1

1

1

0

0

1

ON

PHASE

MODE

DELAY[2]2 DELAY[1]2 DELAY[0]2 nFLTMSK

OK

1

0

0

0

0

0

0

R

Reserved Reserved VSET1[5] VSET1[4] VSET1[3] VSET1[2] VSET1[1] VSET1[0]

0

0

0

1

1

1

1

0

Reserved Reserved VSET2[5] VSET2[4] VSET2[3] VSET2[2] VSET2[1] VSET2[0]

0

0

0

1

1

1

1

0

ON

PHASE

MODE

DELAY[2]2 DELAY[1]2 DELAY[0]2 nFLTMSK

OK

1

0

0

0

0

1

0

R

Reserved Reserved VSET1[5] VSET1[4] VSET1[3] VSET1[2] VSET1[1] VSET1[0]

0

0

0

1

1

0

0

0

Reserved Reserved VSET2[5] VSET2[4] VSET2[3] VSET2[2] VSET2[1] VSET2[0]

0

0

0

1

1

0

0

0

ON PWRSTAT MODE

DELAY[2]2 DELAY[1]2 DELAY[0]2 nFLTMSK

OK

1

0

0

0

0

1

0

R

Reserved Reserved VSET[5]

VSET[4]

VSET[3]

VSET[2] VSET[1]

VSET[0]

0

0

1

1

0

1

0

0

ON

DIS

LOWIQ

DELAY[2]2 DELAY[1]2 DELAY[0]2 nFLTMSK

OK

0

1

0

0

0

0

0

R

Reserved Reserved VSET[5]

VSET[4]

VSET[3]

VSET[2] VSET[1]

VSET[0]

0

0

1

0

0

1

0

0

ON

DIS

LOWIQ

DELAY[2]2 DELAY[1]2 DELAY[0]2 nFLTMSK

OK

0

1

0

0

0

0

0

R

Reserved Reserved VSET[5]

VSET[4]

VSET[3]

VSET[2] VSET[1]

VSET[0]

0

0

1

1

0

1

1

0

ON

DIS

LOWIQ

DELAY[2]2 DELAY[1]2 DELAY[0]2 nFLTMSK

OK

0

1

0

0

0

0

0

R

Reserved Reserved VSET[5]

VSET[4]

VSET[3]

VSET[2] VSET[1]

VSET[0]

0

0

1

1

0

1

1

0

ON

DIS

LOWIQ

DELAY[2]2 DELAY[1]2 DELAY[0]2 nFLTMSK

OK

0

1

0

0

0

0

0

R

Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved

0

1

0

1

0

0

0

0

SUSCHG Reserved TOTTIMO[1] TOTTIMO[0] PRETIMO[1] PRETIMO[0] OVPSET[1] OVPSET[0]

0

1

1

0

1

0

0

0

TIMRSTAT TEMPSTAT INSTAT CHGSTAT TIMRDAT TEMPDAT INDAT

CHGDAT

0

0

0

0

R

R

R

R

TIMRTOT TEMPIN

INCON CHGEOCIN TIMRPRE TEMPOUT INDIS CHGEOCOUT

0

0

0

0

0

0

0

0

Reserved Reserved CSTATE[0] CSTATE[1] Reserved Reserved ACINSTAT Reserved

0

0

R

R

0

R

R

R

: Default values of ACT8931AQJ633.

2: All bits are automatically cleared to default values when the input power is removed or falls below the system UVLO.

Innovative PowerTM

ActivePMUTM and ActivePathTM are trademarks of Active-Semi.

I2CTM is a trademark of NXP.

-9-

www.active-semi.com

Copyright © 2012 Active-Semi, Inc.