EN6360QI-E Просмотр технического описания (PDF) - Enpirion, Inc.

Номер в каталоге

Компоненты Описание

производитель

EN6360QI-E Datasheet PDF : 24 Pages

| |||

EN6360QI

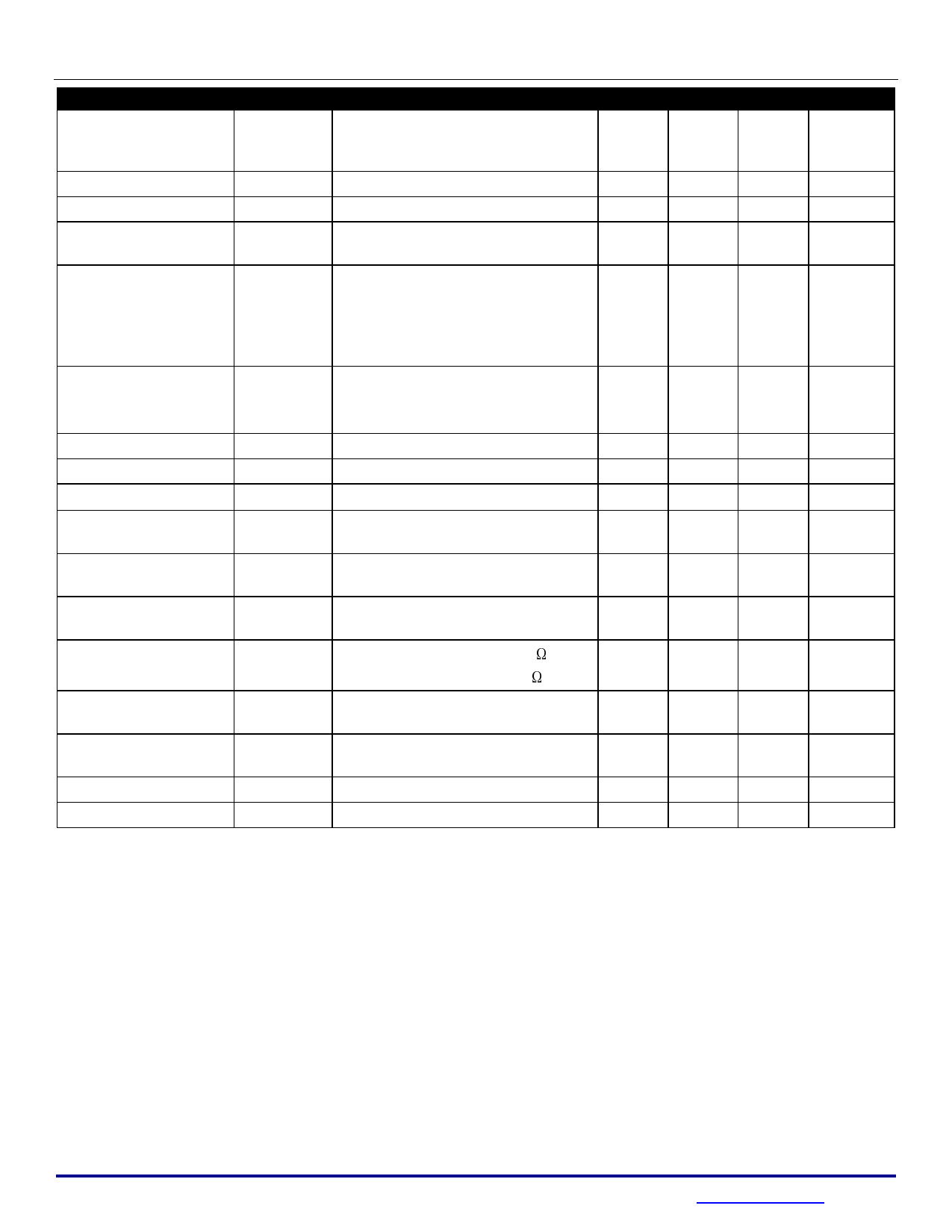

PARAMETER

SYMBOL

TEST CONDITIONS

MIN TYP MAX UNITS

POK Deglitch Delay

VPOK Logic Low level

VPOK Logic high level

POK Internal pull-up

resistor

Falling Edge Deglitch Delay After

Output Crossing 90% level.

FSW=1.2 MHz

With 4mA Current Sink into POK Pin

213

µs

0.4

V

VIN

V

94

kΩ

Current Balance

VOUT Rise Time

Accuracy

With 2 to 4 Converters in Parallel,

the Difference Between Nominal

∆IOUT

and Actual Current Levels.

∆VIN<50mV; RTRACE< 10 mΩ,

+/-10

%

Iload= # Converter * IMAX

∆TRISE

(Note 4)

tRISE [ms] = CSS [nF] x 0.065;

10nF ≤ CSS ≤ 30nF;

(Note 5 and Note 6)

-25

+25

%

ENABLE Logic High

ENABLE Logic Low

VENABLE_HIGH

VENABLE_LOW

2.5V ≤ VIN ≤ 6.6V;

1.2

VIN

V

0

0.8

V

ENABLE Pin Current IEN

VIN = 6.6V

50

µA

M/S Ternary Pin Logic

Low

VT-LOW

Tie M/S Pin to GND

0

0.7

V

M/S Ternary Pin Logic

Float

VT-FLOAT

M/S Pin is Open

1.1

1.4

V

M/S Ternary Pin Logic

Hi (Note 7)

Ternary Pin Input

Current

VT-HIGH

ITERN

Pull Up to VIN through an external

resistor REXT . Refer to Figure 7.

1.8

Ω 2.5V ≤ VIN ≤ 4V, REXT = 15k

Ω 4V < VIN ≤ 6.6V, REXT = 51k

V

117

88

µA

Binary Pin Logic Low

Threshold

VB-LOW

ENABLE, S_IN

0.8

V

Binary Pin Logic High

Threshold

VB-HIGH

ENABLE, S_IN

1.8

V

S_OUT Low Level

S_OUT High Level

VS_OUT_LOW

VS_OUT_HIGH

0.4

V

2.0

V

Note 3: POK threshold when VOUT is rising is nominally 92%. This threshold is 90% when VOUT is falling. After crossing

the 90% level, there is a 256 clock cycle (~213µs at 1.2 MHz) delay before POK is de-asserted. The 90% and 92% levels

are nominal values. Expect these thresholds to vary by ±3%.

Note 4: Parameter not production tested but is guaranteed by design.

Note 5: Rise time calculation begins when AVIN > VUVLO and ENABLE = HIGH.

Note 6: VOUT Rise Time Accuracy does not include soft-start capacitor tolerance..

Note 7: M/S pin is ternary. Ternary pins have three logic levels: high, float, and low. This pin is meant to be strapped to

VIN through an external resistor, strapped to GND, or left floating. The state cannot be changed while the device is on.

©Enpirion 2011 all rights reserved, E&OE

06489

Enpirion Confidential

April 16, 2012

www.enpirion.com, Page 6

Rev: C