GBE-PCS-PM-U1 Просмотр технического описания (PDF) - Lattice Semiconductor

Номер в каталоге

Компоненты Описание

производитель

GBE-PCS-PM-U1 Datasheet PDF : 17 Pages

| |||

Lattice Semiconductor

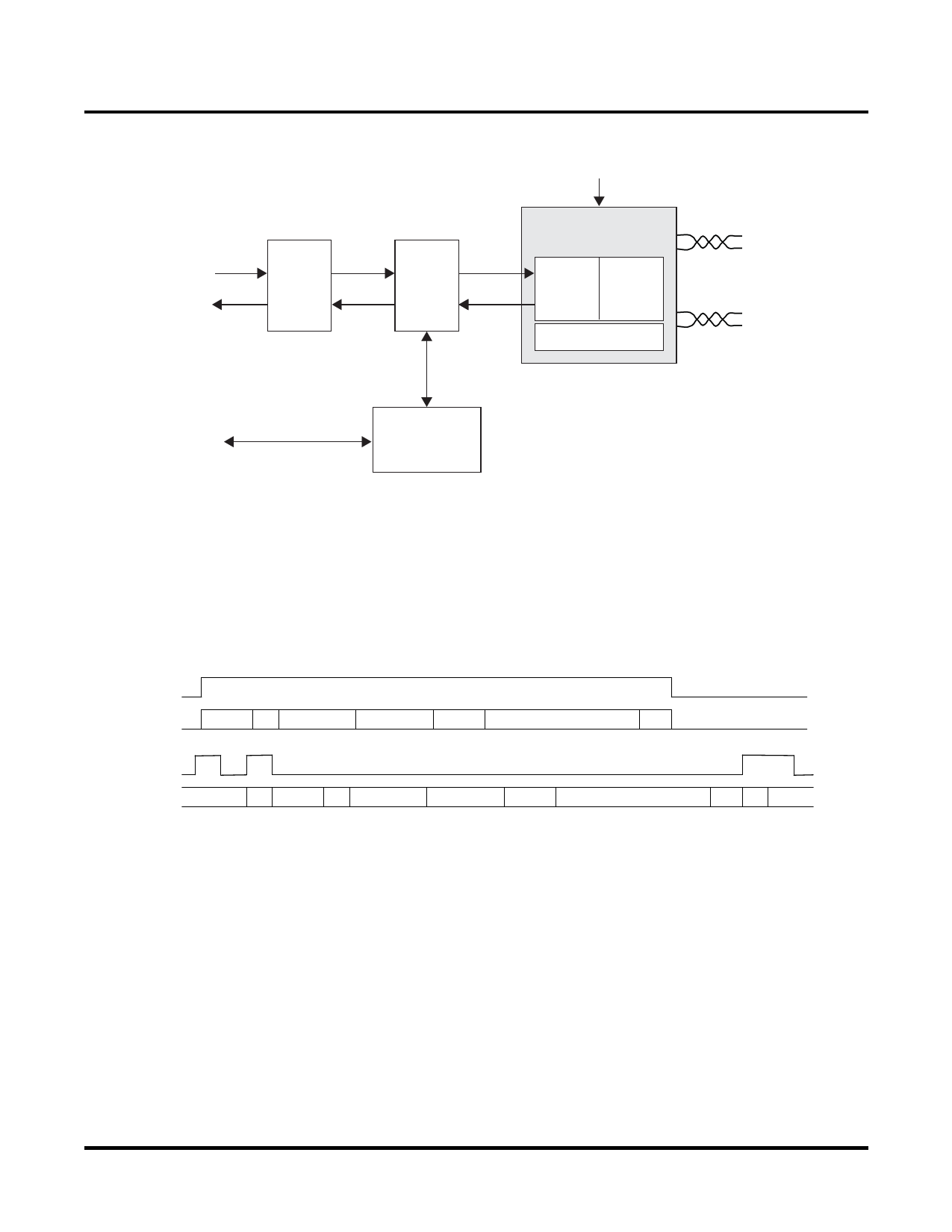

Figure 2. Typical GbE Physical Layer Implementation

Gigabit Ethernet PCS IP Core

for LatticeECP2M

125 MHz

Ref Clk

GMII User I/O

8 bits @

125 MHz

GMII

8 bits @

125 MHz

GbE

PCS

IP Core

8BI

8 bits @

125 MHz

Management

Interface

Part of Embedded

SERDES/PCS

8b10b

Encoder SERDES

Decoder

Serial Interface

to Magnetics

or Backplane

Link State Machine

CML

Differential Pairs

@ 1.25 Gbps

MDIO

Control

Registers

Transmit State Machine

The transmit state machine implements the transmit functions described in clause 36 of the IEEE 802.3 specifica-

tion. The state machine’s main purpose is to convert GMII data frames into code groups. A typical timing diagram

for this circuit block is shown below. Note that the state machine in this IP core does not fully implement the conver-

sion to 10-bit code groups as specified in the 802.3 specification. Instead, partial conversion to 8-bit code groups is

performed. A separate encoder (located in the LatticeECP2M embedded SERDES/PCS block) completes the full

conversion to 10-bit code groups.

Figure 3. Typical Transmit Timing Diagram

tx_en

tx_d preamble SFD Dest Add

Src Add Len/Type

Data

FCS

tx_kcntl

tx_data

IDLE SPD preamble SFD Dest Add

Src Add Len/Type

Data

FCS EPD IDLE

Synchronization State Machine

The synchronization state machine implements the alignment functions described in clause 36 of the IEEE 802.3

specification. The state machine’s main purpose is to determine whether incoming code groups are properly

aligned. Once alignment is attained, proper code groups are passed to the receive state machine. If alignment is

lost for an extended period, an auto negotiation restart is triggered.

Receive State Machine

The receive state machine implements the receive functions described in clause 36 of the IEEE 802.3 specifica-

tion. The state machine’s main purpose is to convert code groups into GMII data frames. A typical timing diagram

for this circuit block is shown below. Note that the state machine in this IP core does not fully implement the conver-

sion from 10-bit code groups as specified in the 802.3 specification. Instead, partial conversion from 8-bit code

groups is performed. A separate decoder (located in the LatticeECP2M embedded SERDES/PCS block) performs

10-bit to 8-bit conversions.

3