ADN4696E(RevA) Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

ADN4696E

(Rev.:RevA)

(Rev.:RevA)

ADN4696E Datasheet PDF : 20 Pages

| |||

Data Sheet

ADN4691E/ADN4693E/ADN4696E/ADN4697E

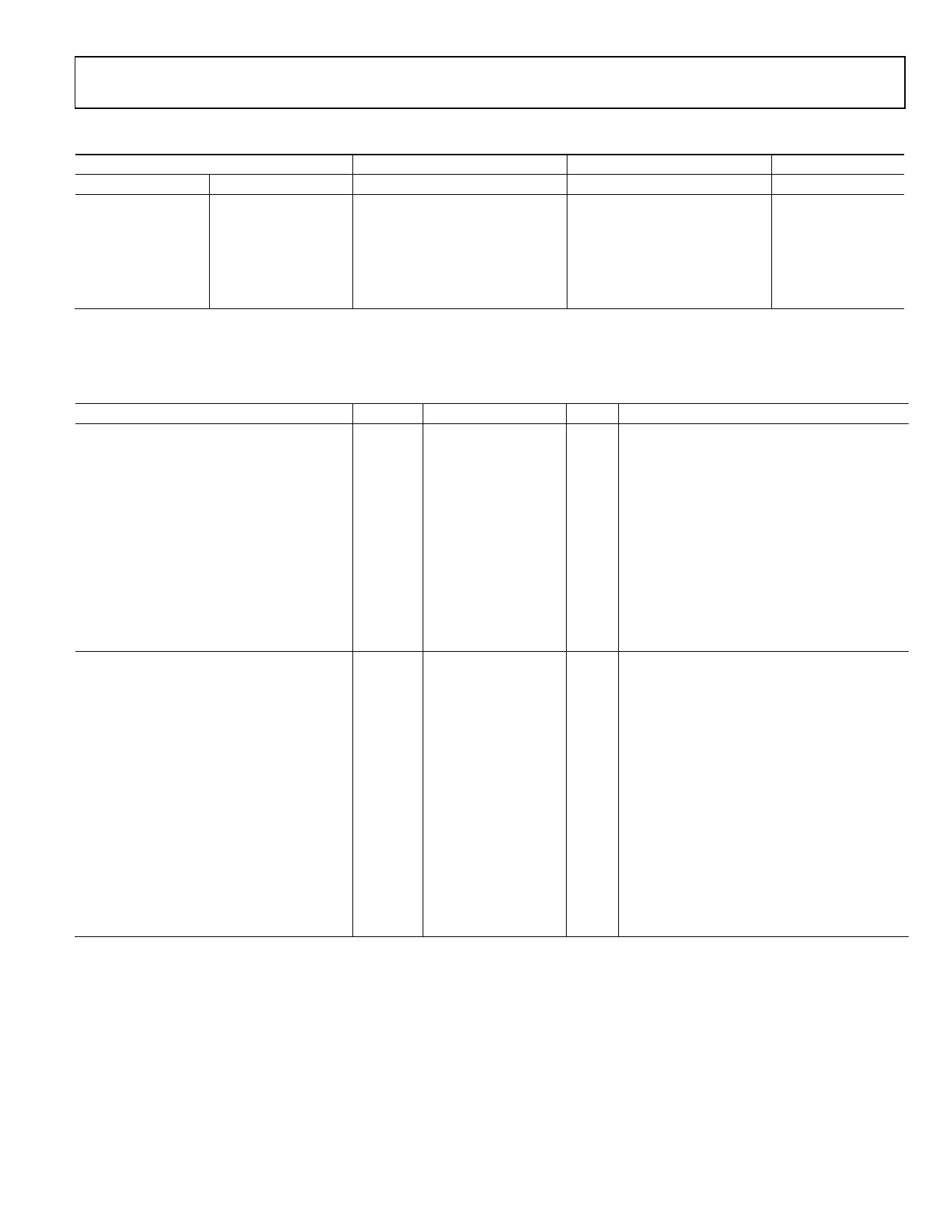

Table 4. Test Voltages for Type 2 Receiver

Applied Voltages

VA (V)

VB (V)

+2.4

0

0

+2.4

+3.8

+3.65

+3.8

+3.75

−1.25

−1.4

−1.35

−1.4

Input Voltage, Differential

VID (V)

+2.4

−2.4

+0.15

+0.05

+0.15

+0.05

Input Voltage, Common Mode

VIC (V)

+1.2

+1.2

+3.725

+3.775

−1.325

−1.375

Receiver Output

RO (V)

H

L

H

L

H

L

TIMING SPECIFICATIONS

VCC = 3.0 V to 3.6 V; TA = TMIN to TMAX, unless otherwise noted.1

Table 5.

Parameter

Symbol Min Typ Max

DRIVER

Maximum Data Rate

200

Propagation Delay

tPLH, tPHL

1

1.5 2.4

Differential Output Rise/Fall Time

tR, tF

1

1.6

Pulse Skew |tPHL – tPLH|

Part-to-Part Skew2

Period Jitter, RMS (1 Standard Deviation)3

Peak-to-Peak Jitter3, 5

tSK

tSK(PP)

tJ(PER)

tJ(PP)

0

100

1

2

3

30 130

Disable Time from High Level

tPHZ

7

Disable Time from Low Level

tPLZ

7

Enable Time to High Level

tPZH

7

Enable Time to Low Level

tPZL

7

RECEIVER

Propagation Delay

tRPLH, tRPHL 2

4

6

Rise/Fall Time

tR, tF

1

2.3

Pulse Skew |tRPHL – tRPLH|

tSK

Type 1 Receiver (ADN4691E,

ADN4693E)

100 300

Type 2 Receiver (ADN4696E,

ADN4697E)

300 500

Part-to-Part Skew2

Period Jitter, RMS (1 Standard Deviation)3

Peak-to-Peak Jitter3, 5

tSK(PP)

tJ(PER)

tJ(PP)

1

4

7

Type 1 Receiver (ADN4691E,

tJ(PP)

ADN4693E)

300 700

Type 2 Receiver (ADN4696E,

ADN4697E)

450 800

Disable Time from High Level

tRPHZ

10

Disable Time from Low Level

tRPLZ

10

Enable Time to High Level

tRPZH

15

Enable Time to Low Level

tRPZL

15

Unit Test Conditions/Comments

Mbps

ns

ns

ps

ns

ps

ps

ns

ns

ns

ns

See Figure 24, Figure 27

See Figure 24, Figure 27

See Figure 24, Figure 27

See Figure 24, Figure 27

100 MHz clock input4 (see Figure 26)

200 Mbps 215 − 1 PRBS input6 (see Figure 29)

See Figure 25, Figure 28

See Figure 25, Figure 28

See Figure 25, Figure 28

See Figure 25, Figure 28

ns

CL = 15 pF (see Figure 30, Figure 33)

ns

CL = 15 pF (see Figure 30, Figure 33)

CL = 15 pF (see Figure 30, Figure 33)

ps

ps

ns

CL = 15 pF (see Figure 30, Figure 33)

ps

100 MHz clock input7 (see Figure 32)

200 Mbps 215 − 1 PRBS input8 (see Figure 35)

ps

ps

ns

See Figure 31, Figure 34

ns

See Figure 31, Figure 34

ns

See Figure 31, Figure 34

ns

See Figure 31, Figure 34

1 All typical values are given for VCC = 3.3 V and TA = 25°C.

2 tSK(PP) is defined as the difference between the propagation delays of two devices between any specified terminals. This specification applies to devices at the same VCC

and temperature, and with identical packages and test circuits.

3 Jitter parameters are guaranteed by design and characterization. Values do not include stimulus jitter.

4 tR = tF = 0.5 ns (10% to 90%), measured over 30,000 samples.

5 Peak-to-peak jitter specifications include jitter due to pulse skew (tSK).

6 tR = tF = 0.5 ns (10% to 90%), measured over 100,000 samples.

7 |VID| = 400 mV (ADN4696E, ADN4697E), Vic = 1.1 V, tR = tF = 0.5 ns (10% to 90%), measured over 30,000 samples.

8 |VID| = 400 mV (ADN4696E, ADN4697E), Vic = 1.1 V, tR = tF = 0.5 ns (10% to 90%), measured over 100,000 samples.

Rev. A | Page 5 of 20