SIT9001AI-43-25E2-20.00000Y Просмотр технического описания (PDF) - Unspecified

Номер в каталоге

Компоненты Описание

производитель

SIT9001AI-43-25E2-20.00000Y Datasheet PDF : 10 Pages

| |||

SiT9001

High Performance Spread Spectrum Oscillator

TThhee SSmmaarrtt TTiimmiinngg CChhooiiccee

Programmable Drive Strength

The SiT9001 includes a programmable drive strength feature

to provide a simple, flexible tool to optimize the clock rise/fall

time for specific applications. Benefits from the programmable

drive strength feature are:

• Improves system radiated electromagnetic interference

(EMI) by slowing down the clock rise/fall time

• Improves the downstream clock receiver’s (RX) jitter by de-

creasing (speeding up) the clock rise/fall time.

• Ability to drive large capacitive loads while maintaining full

swing with sharp edge rates.

For more detailed information about rise/fall time control and

drive strength selection, see the SiTime Applications Note

section; http://www.sitime.com/support/application-notes.

EMI Reduction by Slowing Rise/Fall Time

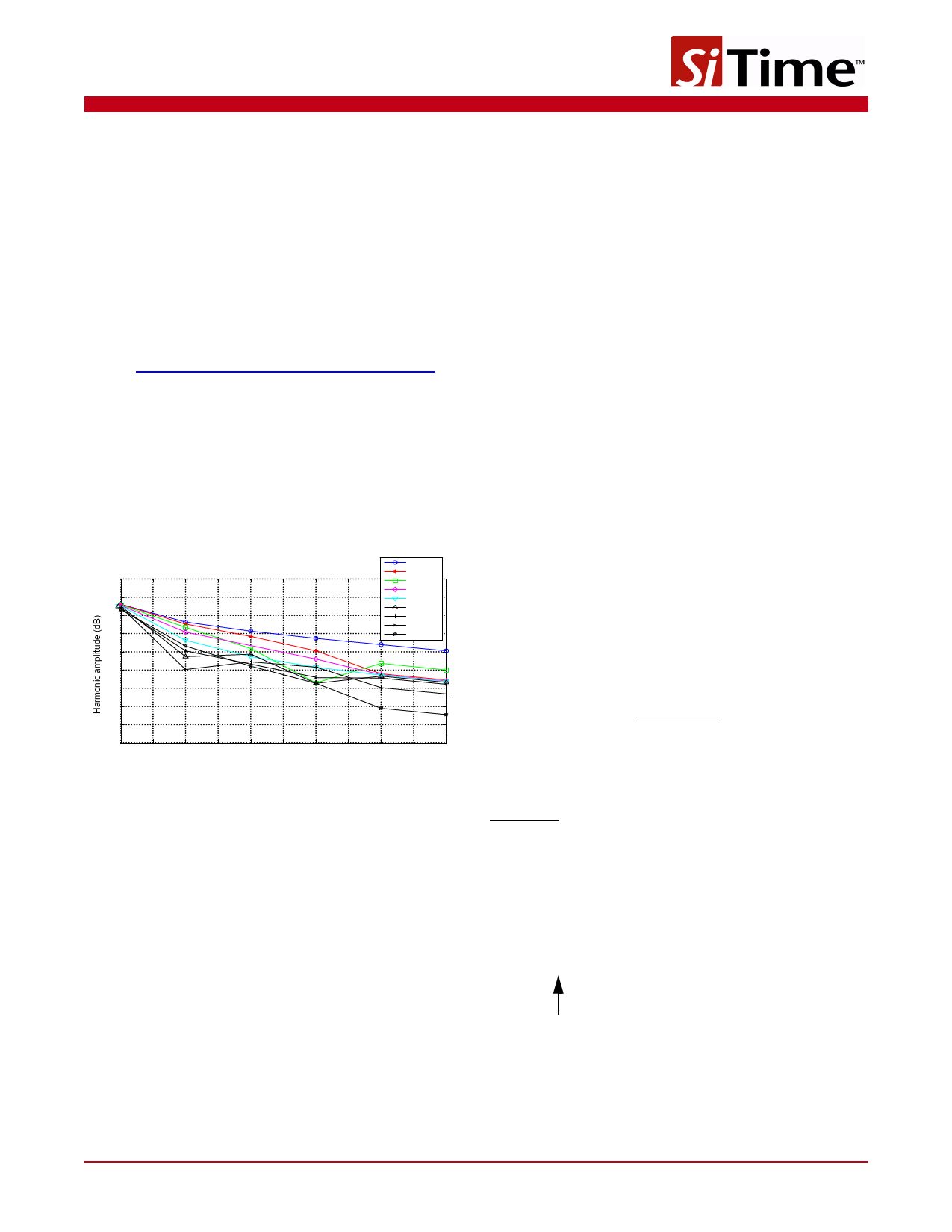

Figure 1 shows the harmonic power reduction as the rise/fall

times are increased (slowed down). The rise/fall times are

expressed as a ratio of the clock period. For the ratio of 0.05,

the signal is very close to a square wave. For the ratio of 0.45,

the rise/fall times are very close to near-triangular waveform.

These results, for example, show that the 11th clock harmonic

can be reduced by 35 dB if the rise/fall edge is increased from

5% of the period to 45% of the period.

10

0

-10

-20

-30

-40

-50

-60

-70

-80 1

3

5

7

Harm onic num ber

t r is e = 0 .0 5

t r is e = 0 .1

t r is e = 0 .1 5

t r is e = 0 .2

t r is e = 0 .2 5

t r is e = 0 .3

t r is e = 0 .3 5

t r is e = 0 .4

t r is e = 0 .4 5

9

11

Figure 1. Harmonic EMI reduction as a Function of

Slower Rise/Fall Time

Jitter Reduction with Faster Rise/Fall Time

Power supply noise can be a source of jitter for the

downstream chipset. One way to reduce this jitter is to

increase rise/fall time (edge rate) of the input clock. Some

chipsets would require faster rise/fall time in order to reduce

their sensitivity to this type of jitter. The SiT9001 provides up

to 3 additional high drive strength settings for very fast rise/fall

time. Refer to the Drive Strength Settings Table to determine

the proper drive strength.

strength, the rise/fall time becomes slower as the output load

increases. As an example, for a 3.3V SiT9001 device with

default drive strength setting, the typical rise/fall time is 1ns for

15 pF output load. The typical rise/fall time slows down to

2.6ns when the output load increases to 45 pF. One can

choose to speed up the rise/fall time to 1.68ns by then

increasing the drive strength setting on the SiT9001.

The SiT9001 can support up to 60 pF or higher in maximum

capacitive loads with up to 3 additional drive strength settings.

Refer to the Drive Strength Settings Table to determine the

proper drive strength for the desired combination of output

load vs. rise/fall time

SiT9001 Drive Strength Selection

The Drive Strength Settings Table define the rise/fall time for

a given capacitive load and supply voltage.

1. Select the table that matches the SiT9001 nominal supply

voltage (1.8V, 2.5V, 2.8V, 3.0V, 3.3V).

2. Select the capacitive load column that matches the appli-

cation requirement (5 pF to 60 pF)

3. Under the capacitive load column, select the desired

rise/fall times.

4. The left-most column represents the part number code for

the corresponding drive strength.

5. Add the drive strength code to the part number for ordering

purposes.

Calculating Maximum Frequency

Based on the rise and fall time data given in Tables 1 through

4, the maximum frequency the oscillator can operate with

guaranteed full swing of the output voltage over temperature

as follows:

M ax Frequency =

1

5 x Trf_20/80

Where Trf_20/80 is the typical rise/fall time at 20% to 80%

Vdd

Example 1

Calculate fMAX for the following condition:

• Vdd = 1.8V

• Capacitive Load: 30 pF

• Desired Tr/f time = 3 ns (rise/fall time part number code = E)

Part number for the above example:

SiT9001AIE14-33E6-123.12345

High Output Load Capability

The rise/fall time of the input clock varies as a function of the

actual capacitive load the clock drives. At any given drive

Drive strength code is inserted here. Default setting is “-”

Rev. 1.2

Page 5 of 9

www.sitime.com