HM3-6514B-9 Просмотр технического описания (PDF) - Intersil

Номер в каталоге

Компоненты Описание

производитель

HM3-6514B-9 Datasheet PDF : 7 Pages

| |||

HM-6514

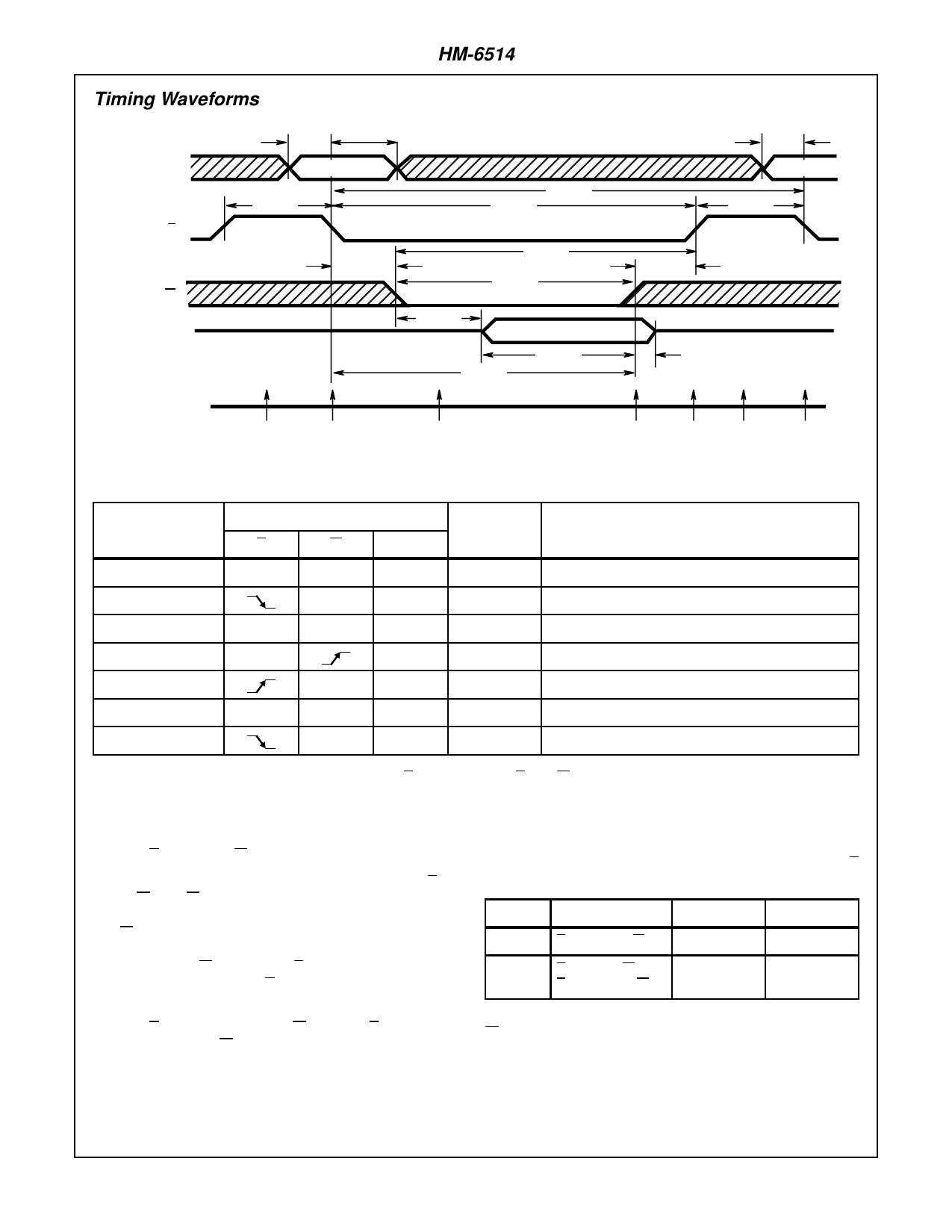

Timing Waveforms (Continued)

TELAX

TAVEL

A

VALID ADD

TEHEL

E

W

HIGH Z

DQ

TELWL

TIME

REFERENCE

-1

0

TELEL

TELEH

TEVAL

NEXT ADD

TEHEL

TWLEH

TWLWH

TWHEH

TWLDV

VALID DATA INPUT

TELWH

TDVWH

HIGH Z

TWHDZ

1

2

3

4

5

TIME

REFERENCE

-1

0

1

2

3

4

5

FIGURE 2. WRITE CYCLE

TRUTH TABLE

INPUTS

E

W

A

DQ

FUNCTION

H

X

X

Z

Memory Disabled

X

V

Z

Cycle Begins, Addresses are Latched

L

L

X

Z

Write Period Begins

L

X

V

Data In is Written

H

X

Z

Write Completed

H

X

X

Z

Prepare for Next Cycle (Same as -1)

X

V

Z

Cycle Ends, Next Cycle Begins (Same as 0)

The write cycle is initiated by the falling edge of E (T = 0),

which latches the address information in the on-chip regis-

ters. There are two basic types of write cycles, which differ in

the control of the common data-in/data-out bus.

Case 1: E falls before W falls

The output buffers may become enabled (reading) if E falls

before W falls. W is used to disable (three-state) the outputs

so input data can be applied. TWLDV must be met to allow

the W signal time to disable the outputs before applying

input data. Also, at the end of the cycle the outputs may

become active if W rises before E. The RAM outputs and all

inputs will three-state after E rises (TEHQZ). In this type of

write cycle TWLEL and TEHWH may be ignored.

Case 2: E falls equal to or after W falls, and E rises before

or equal to W rising

This E and W control timing will guarantee that the data out-

puts will stay disabled throughout the cycle, thus, simplifying

the data input timing. TWLEL and TEHWH must be met, but

TWLDV becomes meaningless and can be ignored. In this

cycle TDVWH and TWHDX become TDVEH and TEHDX. In

other words, reference data setup and hold times to the E

rising edge.

IF

Case 1 E falls before W

Case 2 E falls after W and

E rises before W

OBSERVE

TWLDV

TWLEL

TEHWH

IGNORE

TWLEL

TWLDV

TWHDX

If a series of consecutive write cycles are to be performed,

W may be held low until all desired locations have been writ-

ten (an extension of Case 2).

6-6