MAX3816ACUE Просмотр технического описания (PDF) - Maxim Integrated

Номер в каталоге

Компоненты Описание

производитель

MAX3816ACUE Datasheet PDF : 18 Pages

| |||

I2C 2-Wire Extender for DDC in DVI,

HDMI, and VGA Interfaces

Locally, connect a 47kΩ pullup resistor from CLOCK_C

and DATA_C to VCC. This assumes that a 1.65kΩ

pullup resistor resides at the opposite end of each

channel.

Display Drivers

The display drivers (Figure 11) are typical open-drain

pulldown devices capable of discharging up to 400pF

of capacitive load within the I2C fall-time limits.

Locally, connect a 2.2kΩ pullup resistor from CLOCK_D

and DATA_D to VDD for VDD = 3.3V, or a 3.3kΩ pullup

resistor to VDD for VDD = 5V.

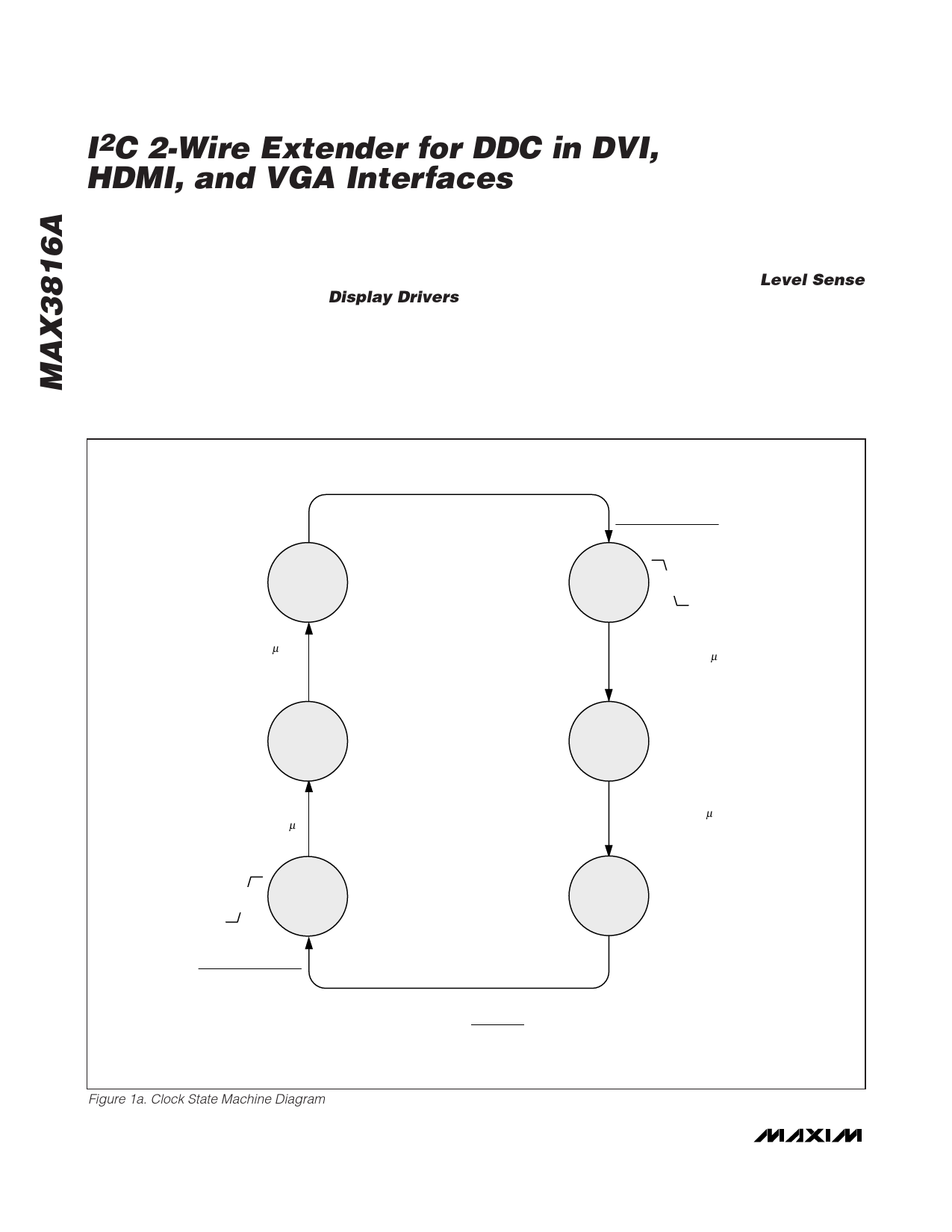

Level Sense

The MAX3816A’s level-sensing circuitry monitors the

incoming data for state transitions. When the CLOCK or

DATA signal is high and drops below VTRIGIH, the con-

troller ramps the outputs low. When the DATA and

CLOCK are low and both rise above VTRIGIL, refer-

enced to GND_REF on the source side or VSS on the

display side, the output drives the level high.

HIGH

STATE

CLOCK_C “OR” CLOCK_D < 75%

1

SENSE ON

DRIVERS OFF

HOLDOFF TIMER ≥ 2.5μs

“AND”

CLOCK_C “AND” CLOCK_D > 85%

6

SENSE OFF

DRIVERS OFF

LOW

STATE

HOLDOFF TIMER = START

2

SENSE OFF

DRIVERS ON

RAMP

DOWN

HOLDOFF TIMER = 1.75μs

3

SENSE OFF

(NOTE 3)

HOLDOFF TIMER = 1.75μs

HOLDOFF TIMER = 2.5μs

RAMP

UP

5

SENSE OFF

DRIVERS ON

4

SENSE ON

(NOTE 3)

HOLDOFF TIMER = START

CLOCK_D > 17.5% AND CLOCK_C > 12.5%

NOTES:

1) STATE CHANGE CONDITIONS ARE IN ITALICS. TRANSITION ACTIONS ARE UNDERLINED.

2) THE DATA CHANNEL STATE MACHINE IS IDENTICAL AND SYMMETRIC, EXCEPT THAT HOLDOFF TIME IS 2.0μs INSTEAD OF 2.5μs.

ALSO, IN ADDITION TO THE 85% CONDITION TO EXIT STATE 6, DATA HAS AN ADDITIONAL EXIT: DATA_C “OR” DATA_D < 60%.

3) DEPENDENT ON MODE PIN 16: MODE = LOW FOR SERIAL OPERATION (DRIVERS HOLD); MODE = HIGH FOR PARALLEL OPERATION (DRIVERS OFF).

Figure 1a. Clock State Machine Diagram

8 _______________________________________________________________________________________