MT90820 Просмотр технического описания (PDF) - Zarlink Semiconductor Inc

Номер в каталоге

Компоненты Описание

производитель

MT90820 Datasheet PDF : 37 Pages

| |||

MT90820

Data Sheet

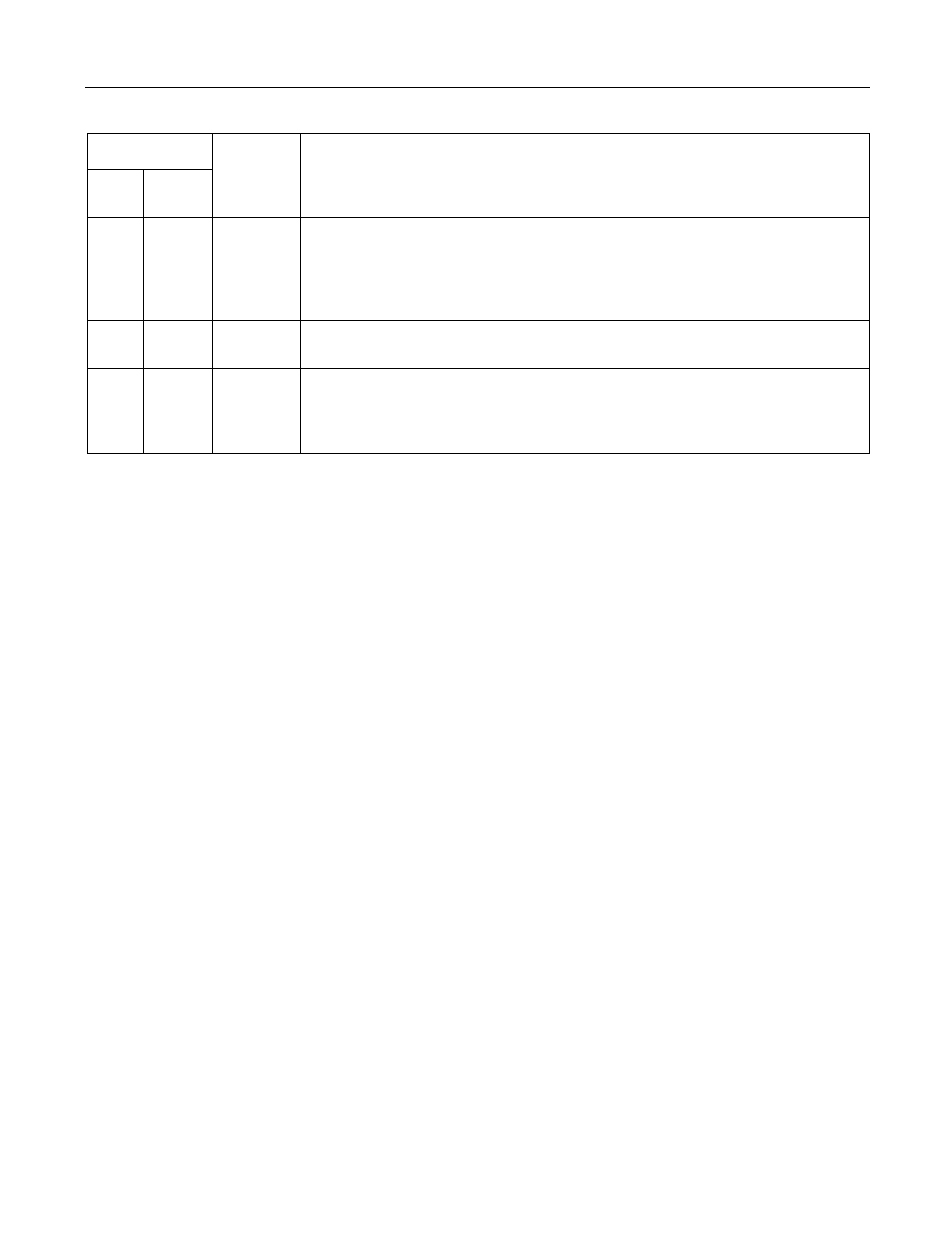

Pin Description

Pin #

84

100

PLCC MQFP

76

57

77 - 84 58-65

-

1 - 4,

27 - 30,

51 - 54

77 - 80

Name

Description

ODE

STo0 - 7

NC

Output Drive Enable (Input): This is the output enable control for the STo0 to STo15

serial outputs. When ODE input is low and the OSB bit of the IMS register is low, STo0-

15 are in a high impedance state. If this input is high, the STo0-15 output drivers are

enabled. However, each channel may still be put into a high impedance state by using the

per channel control bit in the connection memory.

Data Stream Output 0 to 7 (Three-state Outputs): Serial data Output stream. These

streams have selectable data rates of 2.048, 4.096 or 8.192 Mb/s.

No connection.

Device Overview

The MT90820 Large Digital Switch is capable of switching up to 2,048 × 2,048 channels. The MT90820 is designed

to switch 64 kbit/s PCM or N x 64 kbit/s data. The device maintains frame integrity in data applications and

minimum throughput delay for voice applications on a per channel basis.

The serial input streams of the MT90820 can have a bit rate of 2.048, 4.096 or 8.192 Mbit/s and are arranged in

125 µs wide frames, which contain 32, 64 or 128 channels, respectively. The data rates on input and output

streams are identical.

By using Zarlink’s message mode capability, the microprocessor can access input and output time-slots on a per

channel basis. This feature is useful for transferring control and status information for external circuits or other ST-

BUS devices. The MT90820 automatically identifies the polarity of the frame synchronization input signal and

configures its serial streams to be compatible to either ST-BUS or GCI formats.

Two different microprocessor bus interfaces can be selected through the Input Mode pin (IM): Non-multiplexed or

Multiplexed. These interfaces provide compatibility with multiplexed and Motorola non-multiplexed buses.

The frame offset calibration function allows users to measure the frame offset delay using a frame evaluation pin

(FE). The input offset delay can be programmed for individual streams using internal frame input offset registers,

see Table 11.

The internal loopback allows the ST-BUS output data to be looped around to the ST-BUS inputs for diagnostic

purposes.

Functional Description

A functional Block Diagram of the MT90820 is shown in Figure 1.

Data and Connection Memory

For all data rates, the received serial data is converted to parallel format by internal serial-to-parallel converters and

stored sequentially in the data memory. Depending upon the selected operation programmed in the interface mode

select (IMS) register, the useable data memory may be as large as 2,048 bytes. The sequential addressing of the

data memory is performed by an internal counter, which is reset by the input 8 kHz frame pulse (F0i) to mark the

frame boundaries of the incoming serial data streams.

6

Zarlink Semiconductor Inc.