V380SDC Просмотр технического описания (PDF) - QuickLogic Corporation

Номер в каталоге

Компоненты Описание

производитель

V380SDC

V380SDC Datasheet PDF : 13 Pages

| |||

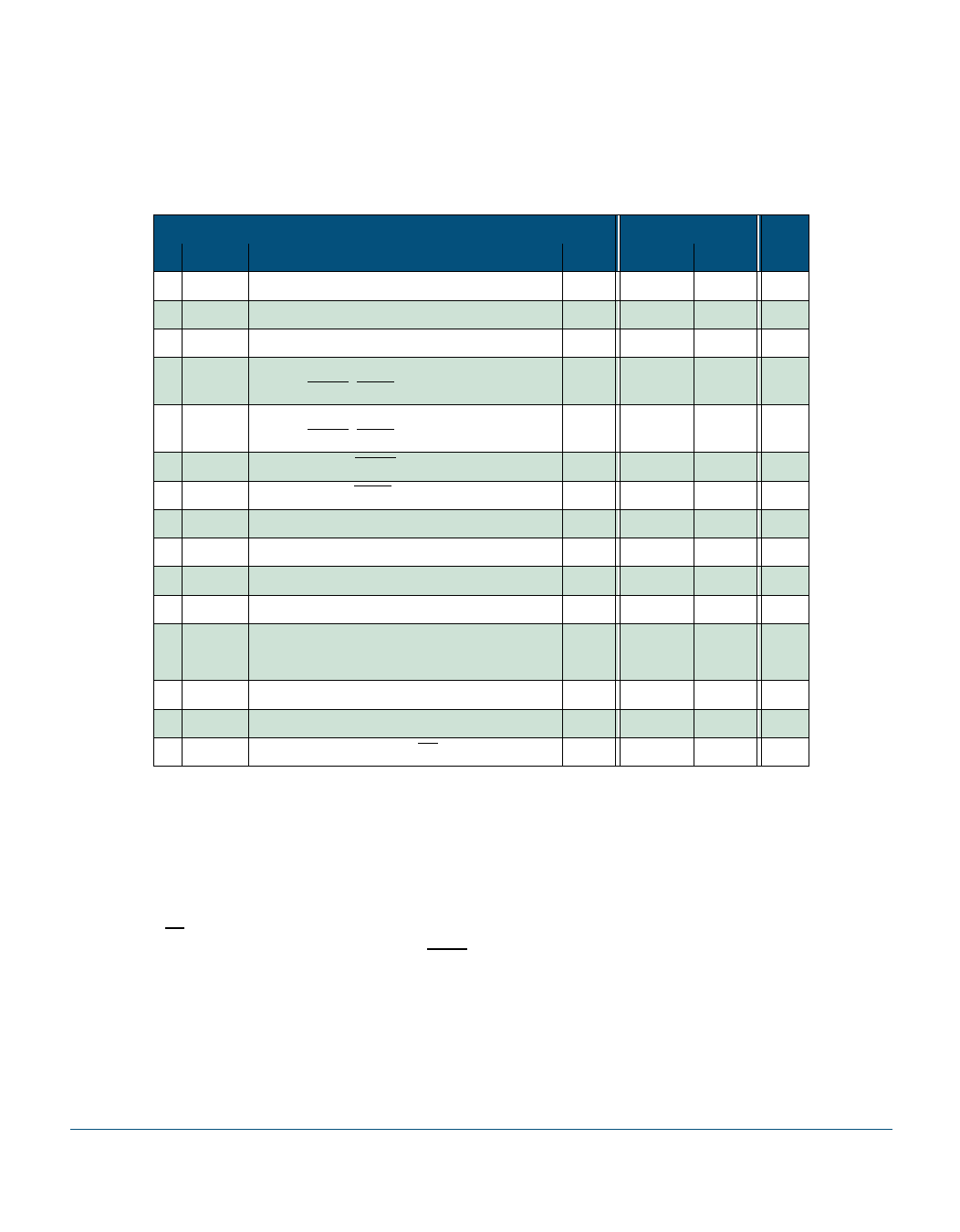

AC Specifications

Pinout

Table 10: Timing Parameters for Vcc = 3.3 Volts ± 5%

# Symbol

Description

1 TC CLK period

2 TCH CLK high time

3 TCL CLK low time

4a

TSU

Synchronous input setup

(except AACK, WAIT)

4b

TSU

Asynchronous input setup

(except AACK, WAIT, IOC[3:0])

4c TSU Input setup for AACK

4d TSU Input setup for WAIT

5 TH Synchronous input hold

6a TCOV CLK to output valid delay (except IOC[3:0])

6b TCOV CLK to output valid delay (IOC[3:0] only)

7 TCOZ CLK to high impedance delay

8 TAS Address Setup to the trailing edge of ALE

9 TAH Address Hold from the trailing edge of ALE

10 TAH Address Hold from the rising edge of CLK

11 TPDQ Propogation Delay from BE to DQM

Notes

75 MHz

Min

Max

13.33

5.5

5.5

Units

ns

ns

ns

1, 8

3

ns

2, 8

7

ns

3

4

ns

4

13

ns

5

1

ns

3

10

ns

3

12

ns

4

11

ns

T--2---c- – 2

ns

2

ns

6

5

ns

7

4

12

ns

Notes:

1 Valid when SYNC bit in the PB_IO_CFG register is set to ‘1’.

2 Valid when SYNC bit in the PB_IO_CFG register is set to ‘0’.

3 Used by the bus watch timer to monitor unclaimed access only.

4 Input through IOC1.

5 Except when in ColdFire MCF5102 mode.

6 Only in ColdFire MCF5102 mode.

7 For BE changing with each datum in a burst write access only.

8 All IOC[3:0] input are synchronous except WAIT.

© 2000 V3 Semiconductor Corp.

V380SDC_A0 Datasheet Rev 1.01 DS-SD01-0101

11