SDA9401 Просмотр технического описания (PDF) - Unspecified

Номер в каталоге

Компоненты Описание

производитель

SDA9401 Datasheet PDF : 69 Pages

| |||

SDA 9401

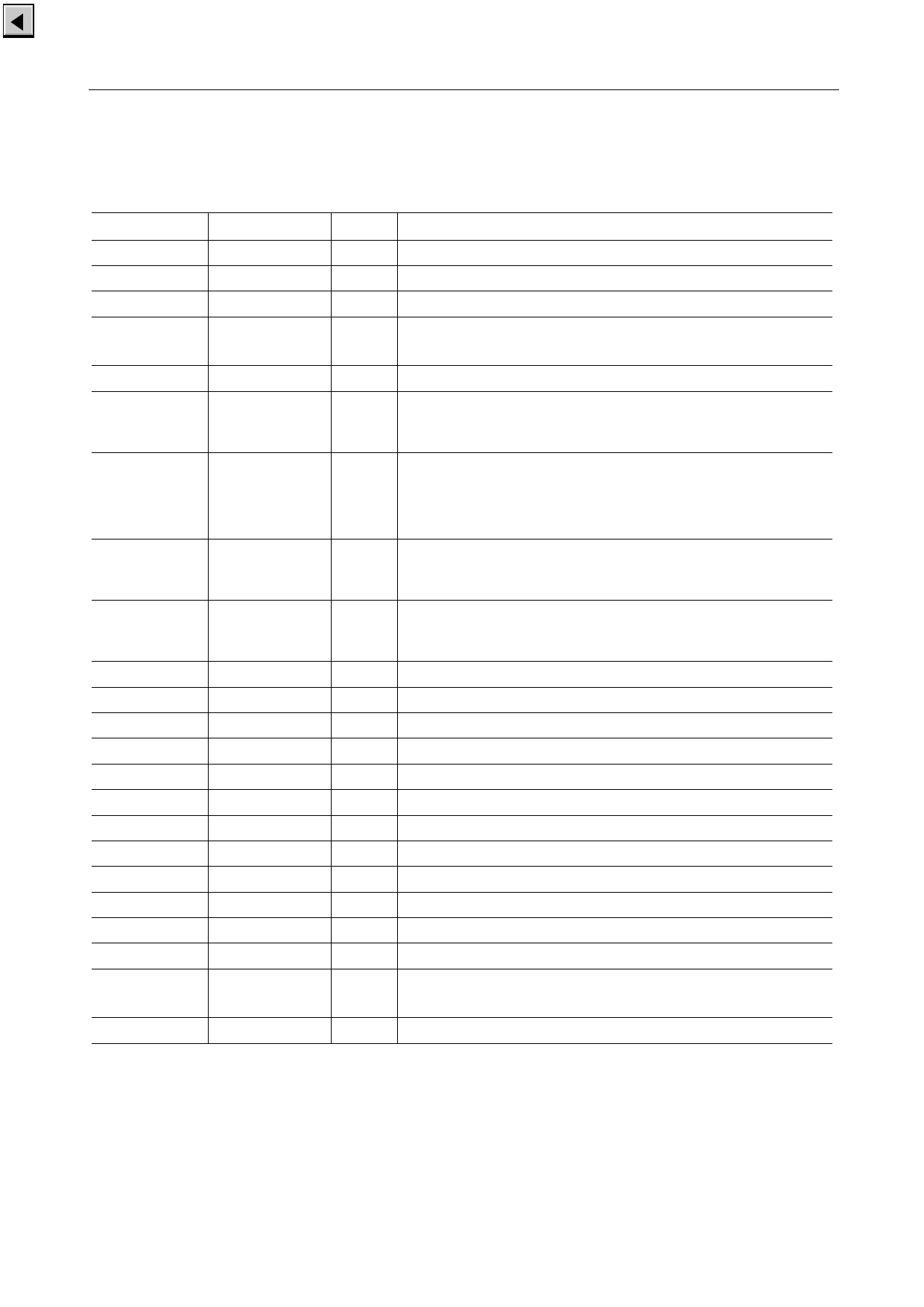

5 Pin description

Pin No.

Name

2,8,24,42,55 VSS1

9,25,41,56 VDD1

36,52,58

VSS2

35,51,53,57, VDD2

59

43,..,50

YIN0...7

31,..,34;37,..., UVIN0...7

40

30

RESET

23

HIN

Type

S

S

S

S

Description

Supply voltage ( VSS = 0 V )

Supply voltage ( VDD = 3.3 V )

Supply voltage ( VSS = 0 V )

Supply voltage ( VDD = 3.3 V )

I/TTL

I/TTL

PD

I/TTL

I/TTL

Data input Y (see input data format)

Data input UV (for 4:2:2 parallel, see input data format)

(for CCIR 656, see input data format)

System reset. The RESET input is low active. In order to

ensure correct operation a "Power On Reset" must be

performed. The RESET pulse must have a minimum

duration of two clock periods of the system clock CLK1.

H-Sync input

PD

(only for full CCIR 656)

22

VIN

I/TTL V-Sync input

29

21

20

54

17,..,10

7,..,3;1;64;63

62

61

60

18

28

27

26

19

SYNCEN

SDA

SCL

CLK1

UVOUT0...7

YOUT0...7

HREF

VOUT

HOUT

INTERLACED

X1 / CLK2

X2

CLKOUT

TEST

PD

(only for full CCIR 656)

I/TTL

I/O

I

Synchronization enable input

I2C-Bus data line (5V ability)

I2C-Bus clock line (5V ability)

I/TTL System clock 1

O/TTL Data output UV (see output data format)

O/TTL Data output Y (see output data format)

O/TTL Horizontal active video output

I/TTL V-Sync output

I/TTL H-Sync output

O/TTL Interlace signal for AC coupled vertical deflection

I/TTL Crystal connection / System clock 2

O/ANA Crystal connection

O/TTL Clock output (depends on I²C parameters CLK11EN,

CLK21EN, see also Clock concept on page 27)

I/TTL Test input, connect to VSS for normal operation

S: supply,

I: input,

O: output, TTL: digital (TTL)

ANA: analog PD: pull down

Micronas

8

Preliminary Data Sheet