ACT5260PC-P10-POD Просмотр технического описания (PDF) - Aeroflex Corporation

Номер в каталоге

Компоненты Описание

производитель

ACT5260PC-P10-POD Datasheet PDF : 10 Pages

| |||

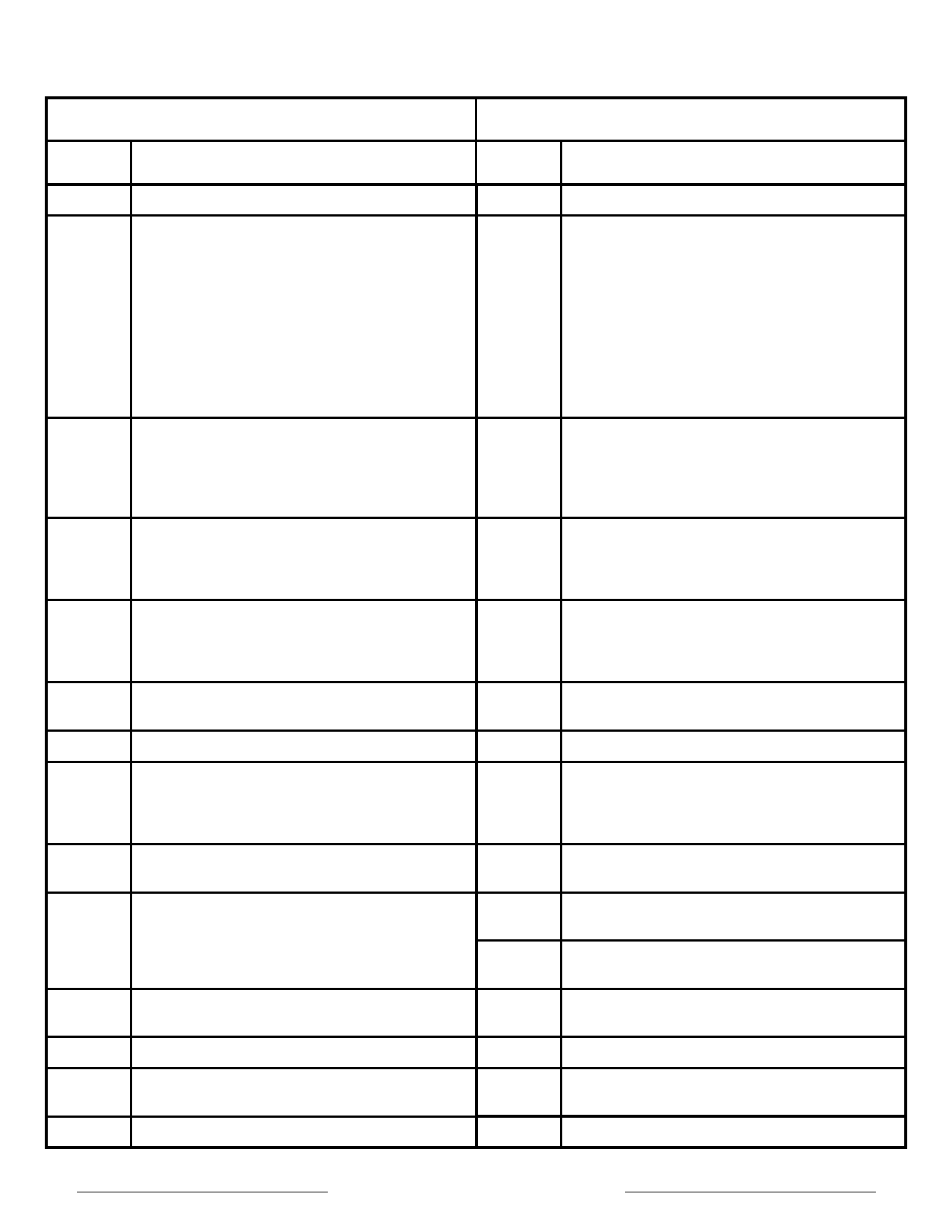

Boot Time Mode Stream Comparison Chart – 5260 vs 4700

5260

Mode Bit

Description

0

4..1

7..5

8

10..9

11

12

14..13

15

Reserved (must be zero)

Write-back data rate

0 → DDDD

1 → DDxDDx

2 → DDxxDDxx

3 → DxDxDxDx

4 → DDxxxDDxxx

5 → DDxxxxDDxxxx

6 → DxxDxxDxxDxx

7 → DDxxxxxxDDxxxxxx

8 → DxxxDxxxDxxxDxxx

9−15 reserved

Pclock to SysClock Multiplier

0 → Multiply by 2, 1 → Multiply by 3

2 → Multiply by 4, 3 → Multiply by 5

4 → Multiply by 6, 5 → Multiply by 7

6 → Multiply by 8, 7 reserved

Specifies byte ordering. Logically ORed with

BigEndian input signal.

0 → Little endian

1 → Big endian

00 → R4000 compatible non-block writes,

01 → reserved,

10 → pipelined non-block writes,

11 → non-block write re-issue

0 → Enable the timer interrupt on Int[5],

1 → Disable the timer interrupt on Int[5].

Reserved: Must be zero (0)

Output driver strength

10 → 100% strength (fastest), 11 → 83%

strength, 00 → 67% strength, 01 → 50%

strength (slowest)

Reserved: Must be zero (0)

17..16 System configuration identifiers - software

visible in processor Config[21..20]

18

21..19

24..22

255..25

0 → Set Timer/Counter to run at Pclock/2

1 → Set Timer/Counter to run at Pclock

Reserved: Must be zero (0)

Write address to write data delay in P cycles

000 → 0 cycles(R5000), ..., 111 → 7 cycles

Reserved: Must be zero (0)

4700

Mode Bit

Description

0

Reserved: Must be zero (0)

4..1 Write-back data rate

0→D

1 → DDx

2 → DDxx

3 → DxDx

4 → DDxxx

5 → DDxxxx

6 → DxxDxx

7 → DDxxxxxx

8 → DxxxDxxx

9−15 reserved

7..5 Clock divisor

0 → 2,1 → 3

2 → 4, 3 → 5

4 → 6, 5 → 7

6 → 8, 7 → reserved

8

0 → Little endian

1 → Big endian

10..9

11

12

14..13

15

16

17

18

255..19

00 → R4000 compatible,

01 → reserved,

10 → pipelined writes,

11 → write re-issue

0 → Enable the timer interrupt on Int[5],

1 → Disable the timer interrupt on Int[5].

Reserved: Must be zero (0)

Output driver strength

10 → 100% strength (fastest), 11 → 83%

strength, 00 → 67% strength, 01 → 50%

strength (slowest)

0 ⇒ TClock[0] enabled,

1 ⇒ TClock[0] disabled

0 ⇒ TClock[1] enabled,

1 ⇒ TClock[1] disabled

0 ⇒ RClock[0] enabled,

1 ⇒ RClock[0] disabled

0 ⇒ RClock[1] enabled,

1 ⇒ RClock[1] disabled

Reserved: Must be zero (0)

Aeroflex Circuit Technology

4

SCD5260PC REV A 9/15/97 Plainview NY (516) 694-6700