SST89E554 Просмотр технического описания (PDF) - Silicon Storage Technology

Номер в каталоге

Компоненты Описание

производитель

SST89E554 Datasheet PDF : 58 Pages

| |||

2.1 Pin Descriptions

FlashFlex51 MCU

SST89E564 / SST89V564 / SST89E554 / SST89V554

Preliminary Specifications

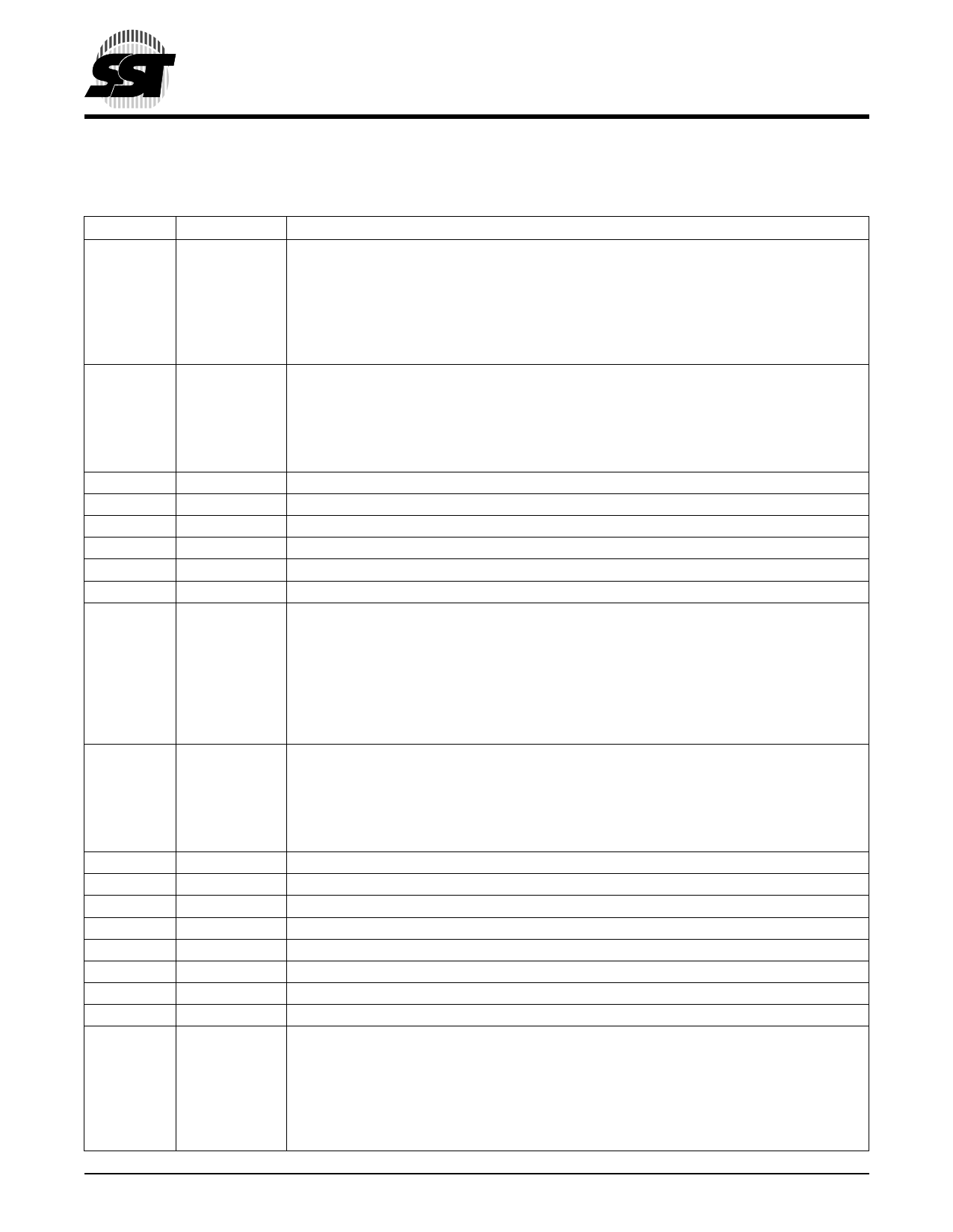

TABLE 2-1: PIN DESCRIPTIONS (1 OF 2)

Symbol

Type1

Name and Functions

P0[7:0]

I/O

Port 0: Port 0 is an 8-bit open drain bi-directional I/O port. As an output port each pin can

sink several LS TTL inputs. Port 0 pins float that have “1”s written to them, and in this state

can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and

data bus during accesses to external memory. In this application, it uses strong internal pull-

ups when transitioning to VOH. Port 0 also receives the code bytes during the external host

mode programming, and outputs the code bytes during the external host mode verification.

External pull-ups are required during program verification.

P1[7:0]

I/O with internal

pull-ups

Port 1: Port 1 is an 8-bit bi-directional I/O port with internal pull-ups. The Port 1 output buffers

can drive LS TTL inputs. Port 1 pins are pulled high by the internal pull-ups when “1”s are

written to them and can be used as inputs in this state. As inputs, Port 1 pins that are exter-

nally pulled low will source current (IIL, see Tables 10-3 and 10-4) because of the internal pull-

ups. P1[5, 6, 7] have high current drive of 16 mA. Port 1 also receives the low-order address

bytes during the external host mode programming and verification.

P1[0]

I/O

T2: External count input to Timer/Counter 2 or Clock-out from Timer/Counter 2

P1[1]

I

T2EX: Timer/Counter 2 capture/reload trigger and direction control

P1[4]

I/O

SS#: Master Input or Slave Output for SPI

P1[5]

I/O

MOSI: Master Output line, Slave Input line for SPI

P1[6]

I/O

MISO: Master Input line, Slave Output line for SPI

P1[7]

I/O

SCK: Master clock output, slave clock input line for SPI

P2[7:0]

I/O with internal

pull-ups

Port 2: Port 2 is an 8-bit bi-directional I/O port with internal pull-ups. Port 2 pins are pulled

high by the internal pull-ups when “1”s are written to them and can be used as inputs in this

state. As inputs, Port 2 pins that are externally pulled low will source current (IIL, see Tables

10-3 and 10-4) because of the internal pull-ups. Port 2 sends the high-order address byte

during fetches from external Program memory and during accesses to external Data Memory

that use 16-bit address (MOVX@DPTR). In this application, it uses strong internal pull-ups

when transitioning to VOH. Port 2 also receives some control signals and a partial of high-

order address bits during the external host mode programming and verification.

P3[7:0]

I/O with internal

pull-ups

Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 3 output buffers

can drive LS TTL inputs. Port 3 pins are pulled high by the internal pull-ups when “1”s are

written to them and can be used as inputs in this state. As inputs, Port 3 pins that are exter-

nally pulled low will source current (IIL, see Tables 10-3 and 10-4) because of the internal pull-

ups. Port 3 also receives some control signals and a partial of high-order address bits during

the external host mode programming and verification.

P3[0]

I

RXD: Serial input line

P3[1]

O

TXD: Serial output line

P3[2]

I

INT0#: External Interrupt 0 Input

P3[3]

I

INT1#: External Interrupt 1 Input

P3[4]

I

T0: External count input to Timer/Counter 0

P3[5]

I

T1: External count input to Timer/Counter 1

P3[6]

O

WR#: External Data Memory Write strobe

P3[7]

O

RD#: External Data Memory Read strobe

PSEN#

I/O

Program Store Enable: PSEN# is the Read strobe to External Program Store. When the

device is executing from Internal Program Memory, PSEN# is inactive (VOH). When the

device is executing code from External Program Memory, PSEN# is activated twice each

machine cycle, except when access to External Data Memory while one PSEN# activation is

skipped in each machine cycle. A forced high-to-low input transition on the PSEN# pin while

the RST input is continually held high for more than ten machine cycles will cause the device

to enter External Host mode for programming.

©2001 Silicon Storage Technology, Inc.

8

S71181-03-000 9/01 384