TQ9303 Просмотр технического описания (PDF) - TriQuint Semiconductor

Номер в каталоге

Компоненты Описание

производитель

TQ9303 Datasheet PDF : 25 Pages

| |||

TQ9303

10b/8b Decoder Block

The 10b/8b Decoder decodes the 10-bit input

(BRXD0..9) into 8 bits, as defined by the Fibre Channel

8b/10b coding scheme. The 10b/8b Decoder drives the

RXERROR (Receiver ERROR) high whenever errors are

detected. There are three types of errors: invalid

characters, invalid running disparities, and special

characters that are not positioned in the most

significant byte of a word. When the 10b/8b Decoder

receives a BRXSYNC of 1, it identifies the input data

byte as a K28.5 character and realigns the data in the

higher order byte of the half word. In Fibre Channel,

K28.5 characters appear only in the most significant

byte of a valid generated parity word. RXERROR remains

high for the word cycle in which the error occurred.

Ordered Set Decoder Block

The Ordered Set Decoder decodes the ordered sets

from the 10b/8b Decoder output. It generates the

decoded ordered set, which is then fed into the mux

along with CRXS0. CRXS0 is a status signal which is

low for a data word and high for an ordered set. The

ordered set decoding table is included in Appendix␣ B.

Word Sync Detector Block

The Word Sync Detector contains a state machine that

monitors the number of valid ordered sets and errors

received. The Word Sync Detector drives WRDSYNCN

low to indicate that word synchronization on the link

has been established. It drives WRDSYNCN high

when word synchronization has been lost.

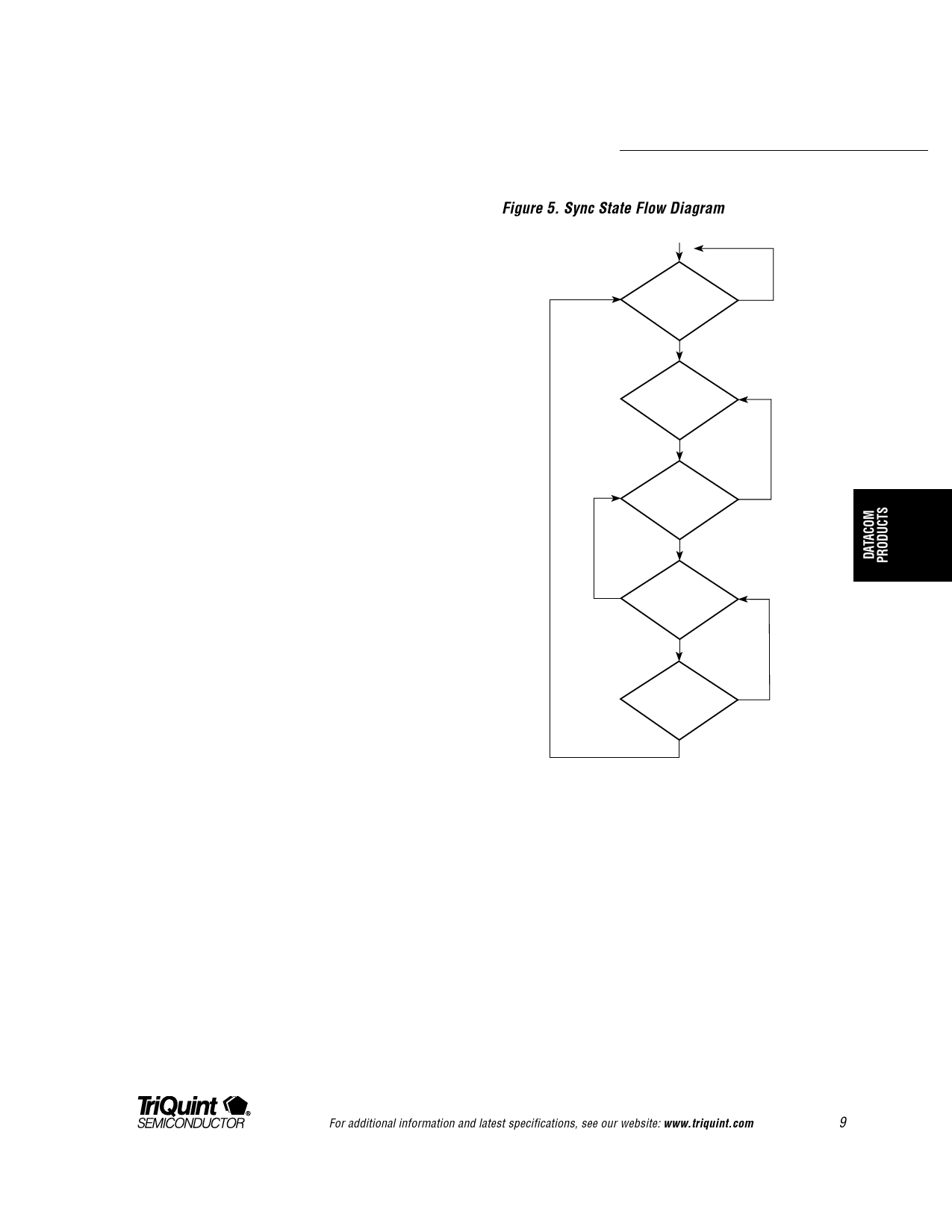

Figure␣ 5 illustrates how word synchronization is

established and lost. The state machine has five states:

State␣ 0␣ – Loss of Word Sync, State␣ 1␣ – Word Sync

Acquired, State␣ 2␣ – 1st Invalid Word, State␣ 3␣ – 2nd

Invalid Word, and State␣ 4␣ – 3rd Invalid Word. Upon

RESET or Raw mode at State␣ 0, the initial condition of

Figure 5. Sync State Flow Diagram

RESET or RAW Mode

STATE 0

Loss of Word Sync

WSYNC = 0

Invalid

Word

Three Ordered Sets

Without Errors

STATE 1

Acquired Word Sync

WSYNC = 1

Invalid Word

STATE 2

1st Invalid Word

WSYNC = 1

Invalid Word

Two Consecutive

Valid Words

Two Consecutive

Valid Words

STATE 3

2nd Invalid Word

WSYNC = 1

Invalid Word

STATE 4

3rd Invalid Word

WSYNC = 1

Invalid Word

Two Consecutive

Valid Words

WRDSYNCN is high. If the Word Sync Detector

receives three consecutive ordered sets without errors,

it acquires word synchronization and moves to State␣ 1,

where WRDSYNCN is driven low. If it receives an

invalid word while in State␣ 1, it moves to State␣ 2 (1st

Invalid Word). If the Word Sync Detector receives an

invalid word while in State␣ 2, it moves to State␣ 3 (2nd

Invalid Word). If, however, it receives two consecutive

valid words, it moves back to State␣ 1. This logic applies

to State␣ 3 and State␣ 4. In State␣ 4 (3rd Invalid Word) if

the Decoder receives an invalid word, it moves to

State␣ 0 (Loss of Word Sync).

For additional information and latest specifications, see our website: www.triquint.com

9