Q67120-C1048 Просмотр технического описания (PDF) - Siemens AG

Номер в каталоге

Компоненты Описание

производитель

Q67120-C1048 Datasheet PDF : 49 Pages

| |||

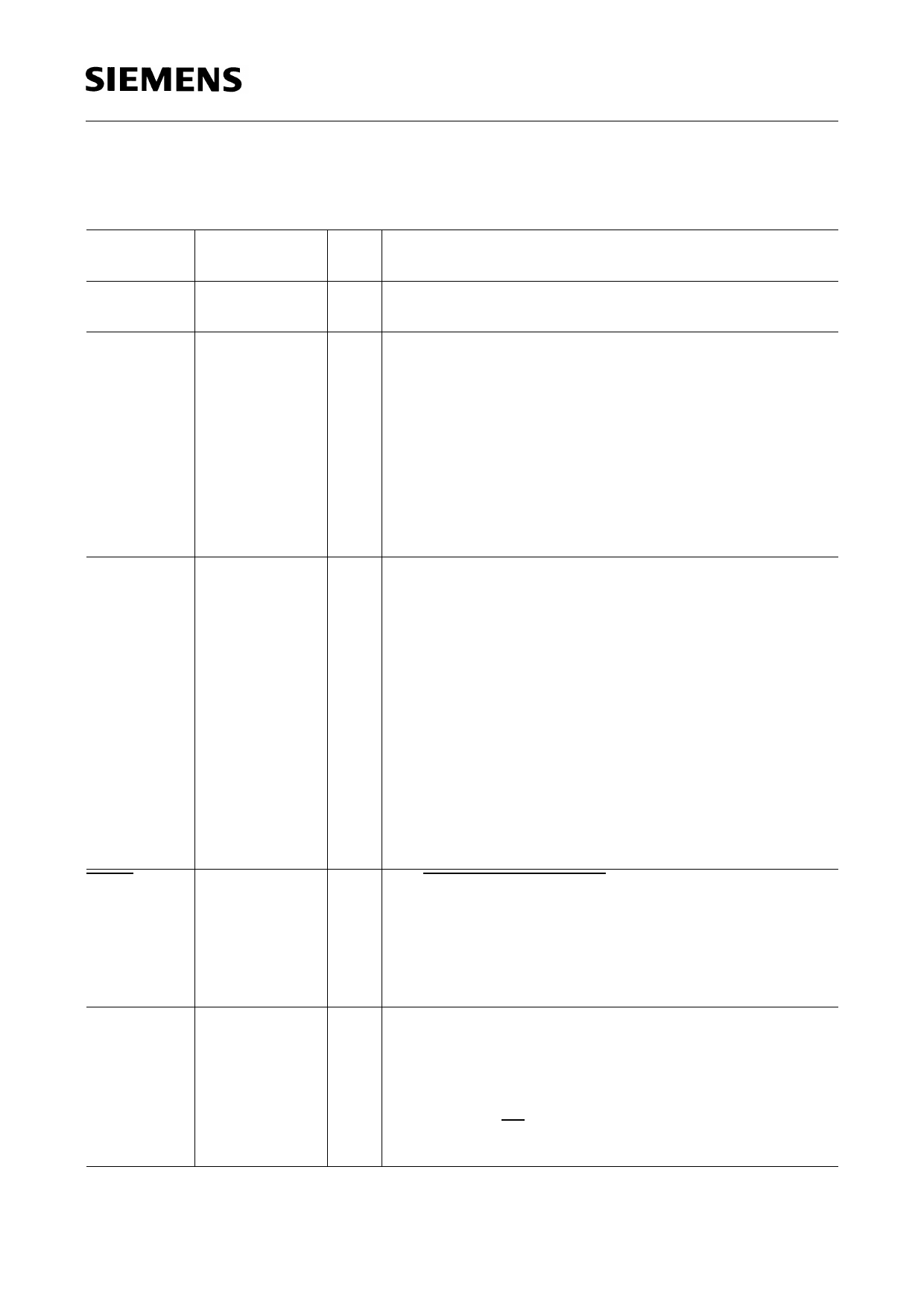

C504

Table 1

Pin Definitions and Functions (cont’d)

Symbol

XTAL2

XTAL1

Pin Number I/O

(P-MQFP-44) *)

14

–

15

–

P2.0-P2.7 18-25

I/O

PSEN

26

O

ALE

27

O

*) I = Input

O = Output

Function

XTAL2

Output of the inverting oscillator amplifier.

XTAL1

Input to the inverting oscillator amplifier and input to the

internal clock generator circuits.

To drive the device from an external clock source, XTAL1

should be driven, while XTAL2 is left unconnected. There

are no requirements on the duty cycle of the external clock

signal, since the input to the internal clocking circuitry is

divided down by a divide-by-two flip-flop. Minimum and

maximum high and low times as well as rise/fall times

specified in the AC characteristics must be observed.

Port 2

is a bidirectional I/O port with internal pullup resistors. Port

2 pins that have 1s written to them are pulled high by the

internal pullup resistors, and in that state can be used as

inputs. As inputs, port 2 pins being externally pulled low

will source current (IIL, in the DC characteris-tics) because

of the internal pullup resistors. Port 2 emits the high-order

address byte during fetches from external program

memory and during accesses to external data memory that

use 16-bit addresses (MOVX @DPTR). In this application

it uses strong internal pullup resistors when issuing 1s.

During accesses to external data memory that use 8-bit

addresses (MOVX @Ri), port 2 issues the contents of the

P2 special function register.

The Program Store Enable

output is a control signal that enables the external program

memory to the bus during external fetch operations. It is

activated every six oscillator periodes except during

external data memory accesses. Remains high during

internal program execution.

The Address Latch Enable

output is used for latching the low-byte of the address into

external memory during normal operation. It is activated

every six oscillator periodes except during an external data

memory access. When instructions are executed from

internal ROM (EA=1) the ALE generation can be disabled

by bit EALE in SFR SYSCON.

Semiconductor Group

9