CTM8B556E Просмотр технического описания (PDF) - CERAMATE TECHNICAL

Номер в каталоге

Компоненты Описание

производитель

CTM8B556E Datasheet PDF : 23 Pages

| |||

CTM8B54E/55E/56E/57E

EPROM-Based 8-Bit CMOS Microcontroller

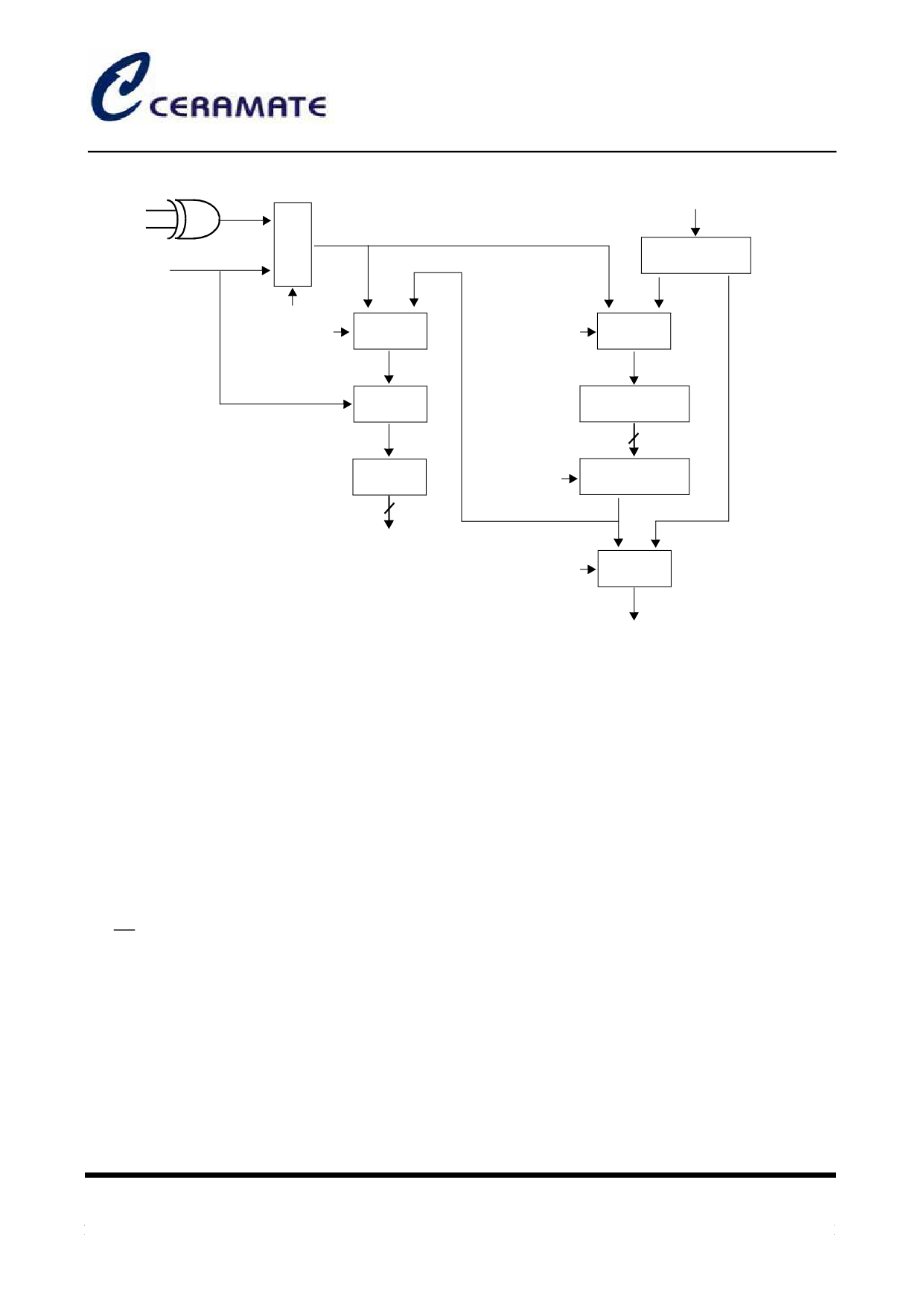

3.5 REAL TIME CLOCK (TIMER0) AND WATCHDOG TIMER

T0CKI

TE

FOSC/4

1M

U

0X

TS

PSC

1

0

MUX

WDT enable

WDT

0

1

PSC MUX

Sync

2 cycles

Timer0

8 bits

Data Bus

8-bit prescaler

8 bits

PS2:PS0 8-to-1 MUX

PSC

1

0

MUX

WDT Time-Out

3.5.1 Timer0

Timer0 is an 8-bit timer/counter. The clock source of Timer0 can come from the internal clock or by an external

clock source presented at the T0CKI pin.

To select the internal clock source, bit 5 of the T0MODE register should be reset. In this mode, Timer0 will

increase by 1 in every instruction cycle (without prescaler).

To select the external clock source, bit 5 of the T0MODE register should be set. In this mode, Timer0 will

increase by 1 on every falling or rising edge of T0CKI pin is controlled by bit 4 of T0MODE register.

3.5.2 Watchdog Timer(WDT)

The Watchdog Timer is a free running on-chip RC oscillator. This RC oscillator is separated from the RC oscil-

lator of the OSCI pin. That means the WDT will keep running even when the oscillator driver is turned off, such

as in sleep mode. During normal operation or in sleep mode, a WDT time-out will cause the device reset and

the TO bit (bit 4 of STATUS register) will be cleared.

Without prescaler, the WDT time-out period is 18ms. This period can be increased by using the prescaler. The

division ratio of prescaler is up to 1:128. Thus, the longest time-out period is approximately 2.3s.

3.5.3 Prescaler

The 8-bit prescaler may be assigned to either the Timer0 or the WDT through the PSC bit (bit 3 of the

T0MODE register). Setting this bit assigns the prescaler to the WDT. Resetting this bit assigns the prescaler to

the Timer0. The PS2:PS0 bits determine the prescale ratio. When assigned to Timer0, the prescaler will be

cleared by instructions which write to Timer0 Register. A CLRWDT instruction will clear the WDT and pres-

caler when assigned to WDT. The prescaler can not be assigned to both the Timer0 and WDT simultaneously.

* All specs and applications shown above subject to change without prior notice.

1F-5 NO.66 SEC.2 NAN-KAN RD ., LUCHU , TAOYUAN, TAIWAN, R.O.C

Email: server@ceramate.com.tw

Tel:886-3-3529445

Fax:886 -3 -3521052

Page 10 of 23

Http: www.ceramate.com.tw

Rev 1.1 Dec 26,2001