ADUM1100 Просмотр технического описания (PDF) - Analog Devices

Номер в каталоге

Компоненты Описание

производитель

ADUM1100 Datasheet PDF : 20 Pages

| |||

ADuM1100

Data Sheet

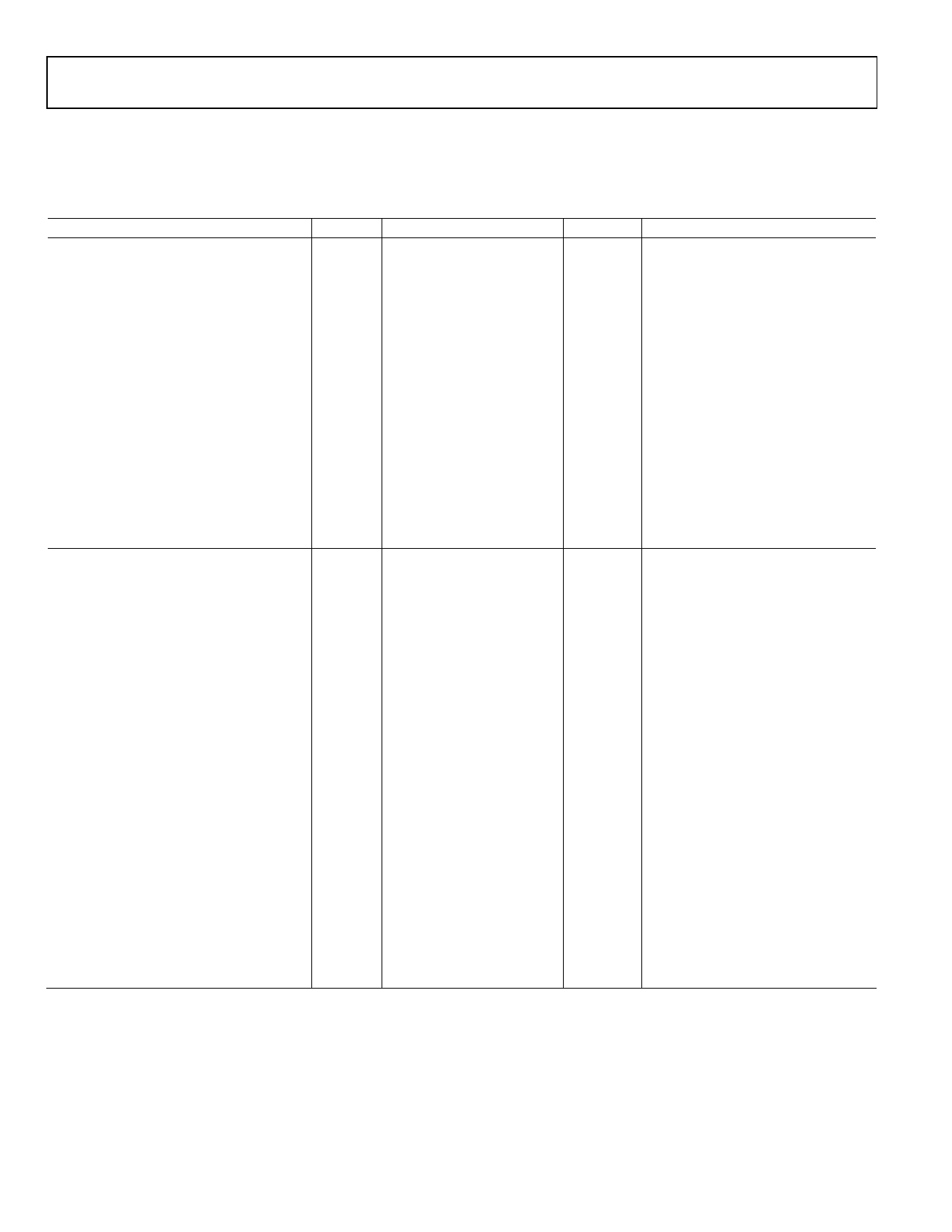

ELECTRICAL SPECIFICATIONS—3.3 V OPERATION

All voltages are relative to their respective ground. 3.0 V ≤ VDD1 ≤ 3.6 V, 3.0 V ≤ VDD2 ≤ 3.6 V. All minimum/maximum specifications apply

over the entire recommended operation range, unless otherwise noted. All typical specifications are at TA = 25°C, VDD1 = VDD2 = 3.3 V.

Table 2.

Parameter

Symbol Min

Typ Max Unit

Test Conditions

DC SPECIFICATIONS

Input Supply Current

IDD1 (Q)

0.1

0.3 mA

VI = 0 V or VDD1

Output Supply Current

IDD2 (Q)

0.005 0.04 mA

VI = 0 V or VDD1

Input Supply Current (25 Mbps)

(See Figure 5)

IDD1 (25)

2.0

2.8 mA

12.5 MHz logic signal frequency

Output Supply Current1 (25 Mbps)

(See Figure 6)

IDD2 (25)

0.3

0.7 mA

12.5 MHz logic signal frequency

Input Supply Current (50 Mbps)

(See Figure 5)

IDD1 (50)

4.0

6.0 mA

25 MHz logic signal frequency,

ADuM1100BR/ADuM1100UR only

Output Supply Current1 (50 Mbps)

(See Figure 6)

IDD2 (50)

1.2

1.6 mA

25 MHz logic signal frequency,

ADuM1100BR/ADuM1100UR only

Input Current

II

−10

+0.01 +10 μA

0 V ≤ VIN ≤ VDD1

Logic High Output Voltage

VOH

VDD2 − 0.1 3.3

V

IO = −20 μA, VI = VIH

VDD2 − 0.5 3.0

V

IO = −2.5 mA, VI = VIH

Logic Low Output Voltage

VOL

0.0

0.1 V

IO = 20 μA, VI = VIH

0.04 0.1 V

IO = 400 μA, VI = VIH

0.3

0.4 V

IO = 2.5 mA, VI = VIH

SWITCHING SPECIFICATIONS

For ADuM1100AR

Minimum Pulse Width2

Maximum Data Rate3

PW

25

40 ns

Mbps

CL = 15 pF, CMOS signal levels

CL = 15 pF, CMOS signal levels

For ADuM1100BR/ADuM1100UR

Minimum Pulse Width2

Maximum Data Rate3

PW

50

10

20 ns

100

Mbps

CL = 15 pF, CMOS signal levels

CL = 15 pF, CMOS signal levels

For All Grades

Propagation Delay Time to Logic Low tPHL

Output4, 5 (See Figure 8)

14.5 28 ns

CL = 15 pF, CMOS signal levels

Propagation Delay Time to Logic

tPLH

High Output4, 5 (See Figure 8)

15.0 28 ns

CL = 15 pF, CMOS signal levels

Pulse Width Distortion |tPLH − tPHL|5

Change vs. Temperature6

PWD

0.5

3

10

ns

ps/°C

CL = 15 pF, CMOS signal levels

CL = 15 pF, CMOS signal levels

Propagation Delay Skew

tPSK1

(Equal Temperature)5, 7

15 ns

CL = 15 pF, CMOS signal levels

Propagation Delay Skew

tPSK2

(Equal Temperature, Supplies)5, 7

12 ns

CL = 15 pF, CMOS signal levels

Output Rise/Fall Time

tR, tF

3

ns

CL = 15 pF, CMOS signal levels

Common-Mode Transient Immunity |CML|,

25

35

at Logic Low/High Output8

|CMH|

kV/μs

VI = 0 V or VDD1, VCM = 1000 V,

transient magnitude = 800 V

Refresh Rate

Input Dynamic Supply Current9

Output Dynamic Supply Current9

fr

IDDI (D)

IDDO (D)

1.1

Mbps

0.08

mA/Mbps

0.04

mA/Mbps

Rev. I | Page 6 of 20