FT8010 Просмотр технического описания (PDF) - Fairchild Semiconductor

Номер в каталоге

Компоненты Описание

производитель

FT8010 Datasheet PDF : 13 Pages

| |||

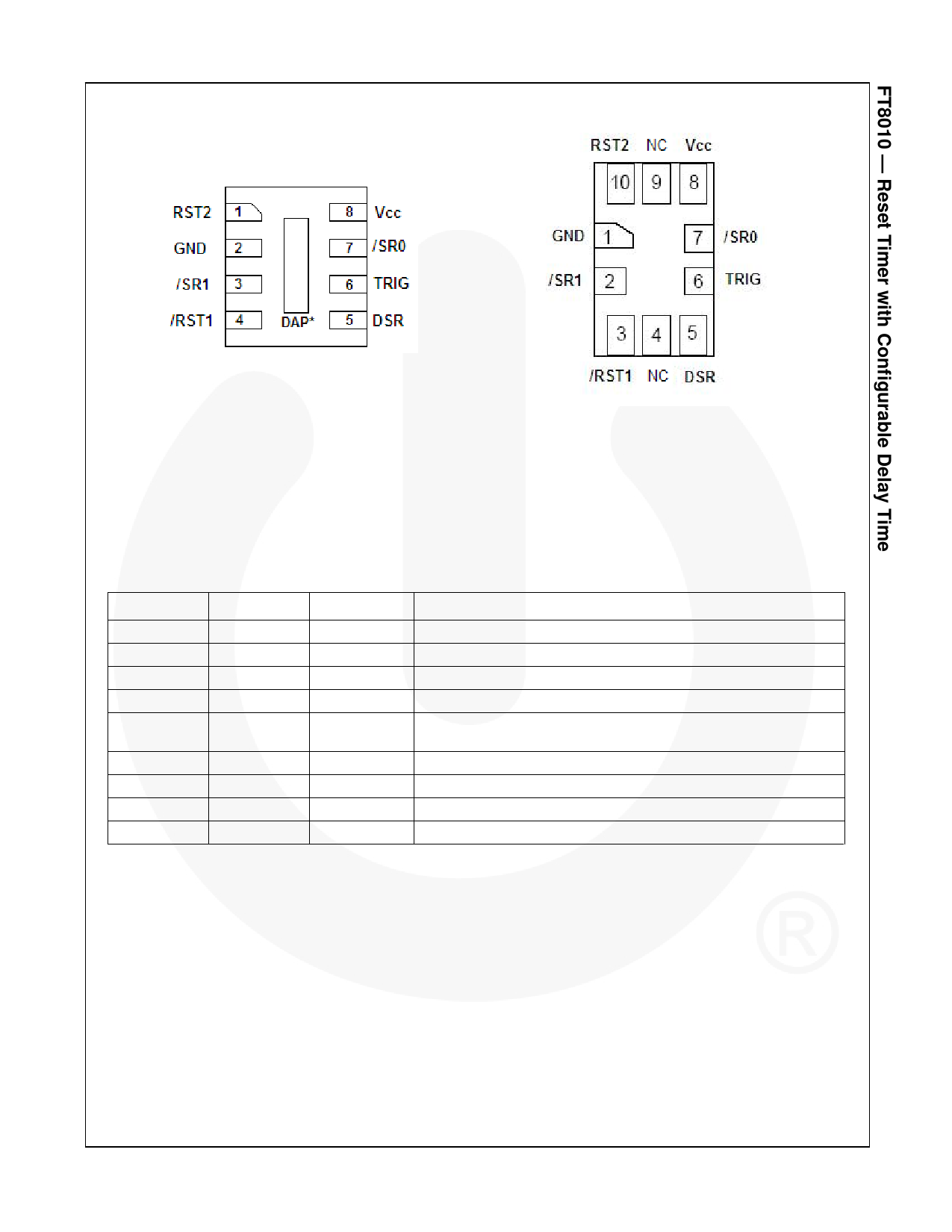

Pin Configuration

Figure 2.

MLP Pin Configuration(1)

(Top Through View)

Note:

1. The DAP may be a no connect or it may be tied to ground.

2. NC = No connect

Figure 3.

UMLP Pin Configuration(2)

(Top Through View)

Pin Definitions

MLP Pin #

1

2

3

4

UMLP Pin #

10

1

2

3

5

5

6

6

7

7

8

8

4, 9,

Name

RST2

GND

/SR1

/RST1

DSR

TRIG

/SR0

VCC

NC

Description

Push-Pull Output, Active HIGH

Ground

Secondary Reset Input, Active LOW

Open-Drain Output, Active LOW

Delay Selection Input (Must be tied directly to GND or VCC; do not

use pull-up or pull-down resistors.)

Test Pin, Tied to GND in Normal Use

Primary Reset Input, Active LOW

Power Supply

No Connect

© 2009 Fairchild Semiconductor Corporation

FT8010 • Rev. 1.0.7

3

www.fairchildsemi.com