MT90737 Просмотр технического описания (PDF) - Mitel Networks

Номер в каталоге

Компоненты Описание

производитель

MT90737 Datasheet PDF : 40 Pages

| |||

MT90737 CMOS

Preliminary Information

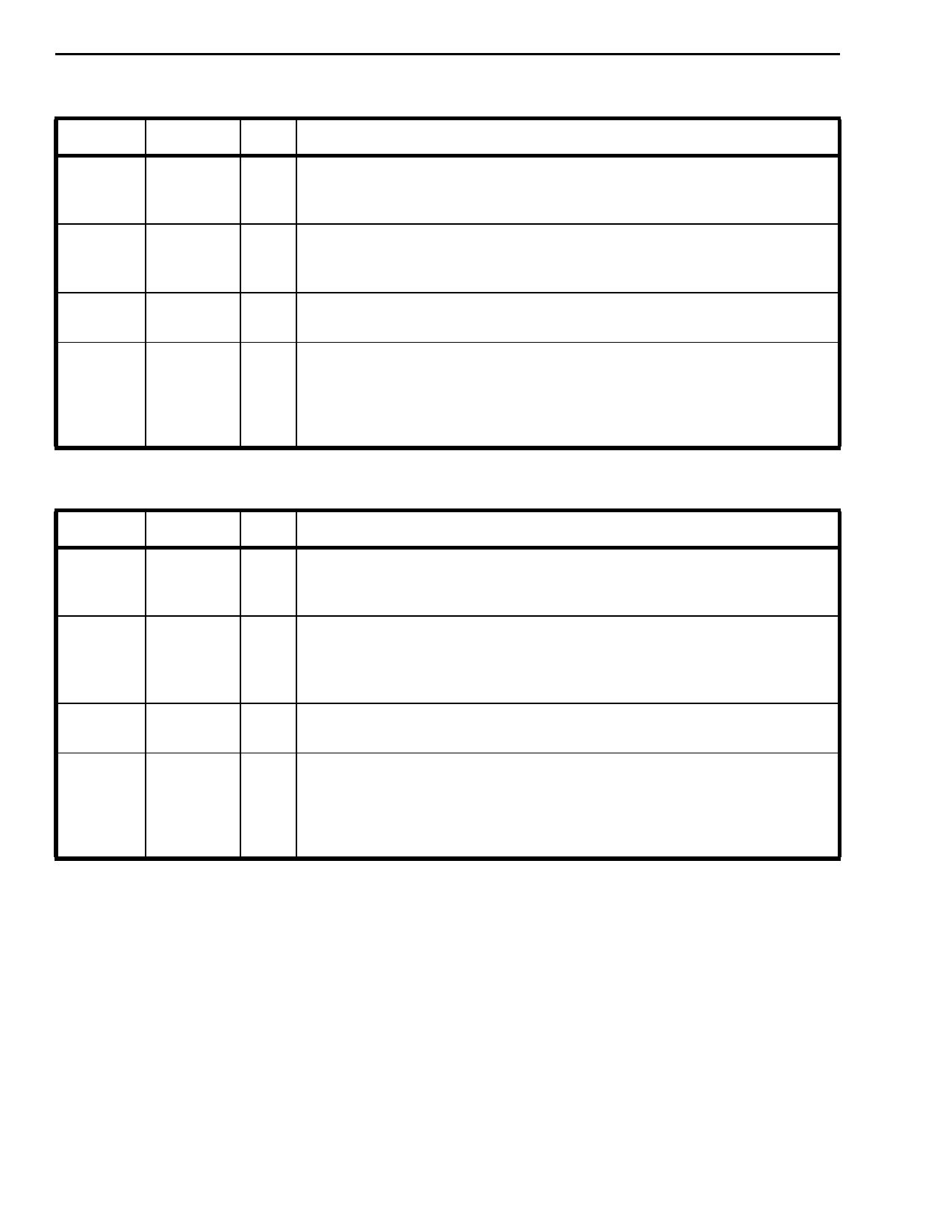

Receive C-Bit Interface

Pin #

Name I/O/P

Description

65

CCKR

O Receive C-Bit Clock. TTL Type IV compatible. A gapped clock signal pro-

vided for clocking out the selected receive C-bit data. Data (CDR) is clocked

out on positive transitions.

66

CDR

O Receive C-Bit Data. TTL Type IV compatible. The following C-bits are pro-

vided at this interface. C2, C3, C4, C5, C6, C13, C14, C15, C16, C17, C18,

C19, C20, and C21.

64

CFMR

O Receive C-Bit Framing Pulse. TTL Type IV compatible. This positive framing

pulse occurs prior to the C2 bit.

61

CDCCR

O Receive Data Link Indication. TTL Type IV compatible. A positive pulse that

identifies the location of the three data link C-bits (C13, C14, and C15). The

receive C-bit clock (CCKR) may be AND’ed with this signal to provide a

gapped data link clock for loading the three C-bits from the C-bit data (CDR)

into external circuitry. CDCCR is enabled by placing a high on DLEN pin.

Note: I = Input; O = Output; P = Power. See DC Characteristics section for CMOS and TTL Type definitions.

Transmit C-Bit Interface

Pin #

Name I/O/P

Description

92

CCKT

O Transmit C-Bit Clock. TTL Type IV compatible. A gapped clock signal pro-

vided for clocking in selected transmit C-bit data (CDT). Data is clocked into

the MT90737 on positive transitions.

89

CDT

I Transmit C-Bit Data. TTL Type I compatible. The transmit gapped clock

(CCKT) provided for clocking in the following C-bits: C2, C4, C5, C6, C13,

C14, C15, C16, C17, C18, C19, C20, and C21. An unused C-bit should be

transmitted as a one.

91

CFMT

O Transmit C-Bit Framing Pulse. TTL Type IV compatible. This positive fram-

ing pulse occurs prior to the C2 bit.

198

CDCCT

O Transmit Data Link Indication. TTL Type IV compatible. A positive pulse that

identifies the location of the three data link C-bits (C13, C14, and C15). The

transmit C-bit clock (CCKT) may be AND’ed with this signal to provide a

gapped data link clock signal. CDCCT is enabled by placing a high on DLEN

pin.

Note: I = Input; O = Output; P = Power. See DC Characteristics section for CMOS and TTL Type definitions.

5-70