X24C01 Просмотр технического описания (PDF) - Xicor -> Intersil

Номер в каталоге

Компоненты Описание

производитель

X24C01 Datasheet PDF : 14 Pages

| |||

X24C01

Sequential Read

Sequential read is initiated in the same manner as the

byte read. The first data byte is transmitted as with the

byte read mode, however, the master now responds

with an acknowledge, indicating it requires additional

data. The X24C01 continues to output data for each

acknowledge received. The read operation is termi-

nated by the master; by not responding with an acknowl-

edge and by issuing a stop condition.

The data output is sequential, with the data from address

n followed by the data from n + 1. The address counter

for read operations increments all address bits, allowing

the entire memory contents to be serially read during

one operation. At the end of the address space (address

127) the counter “rolls over” to zero and the X24C01

continues to output data for each acknowledge re-

ceived. Refer to Figure 8 for the address, acknowledge

and data transfer sequence.

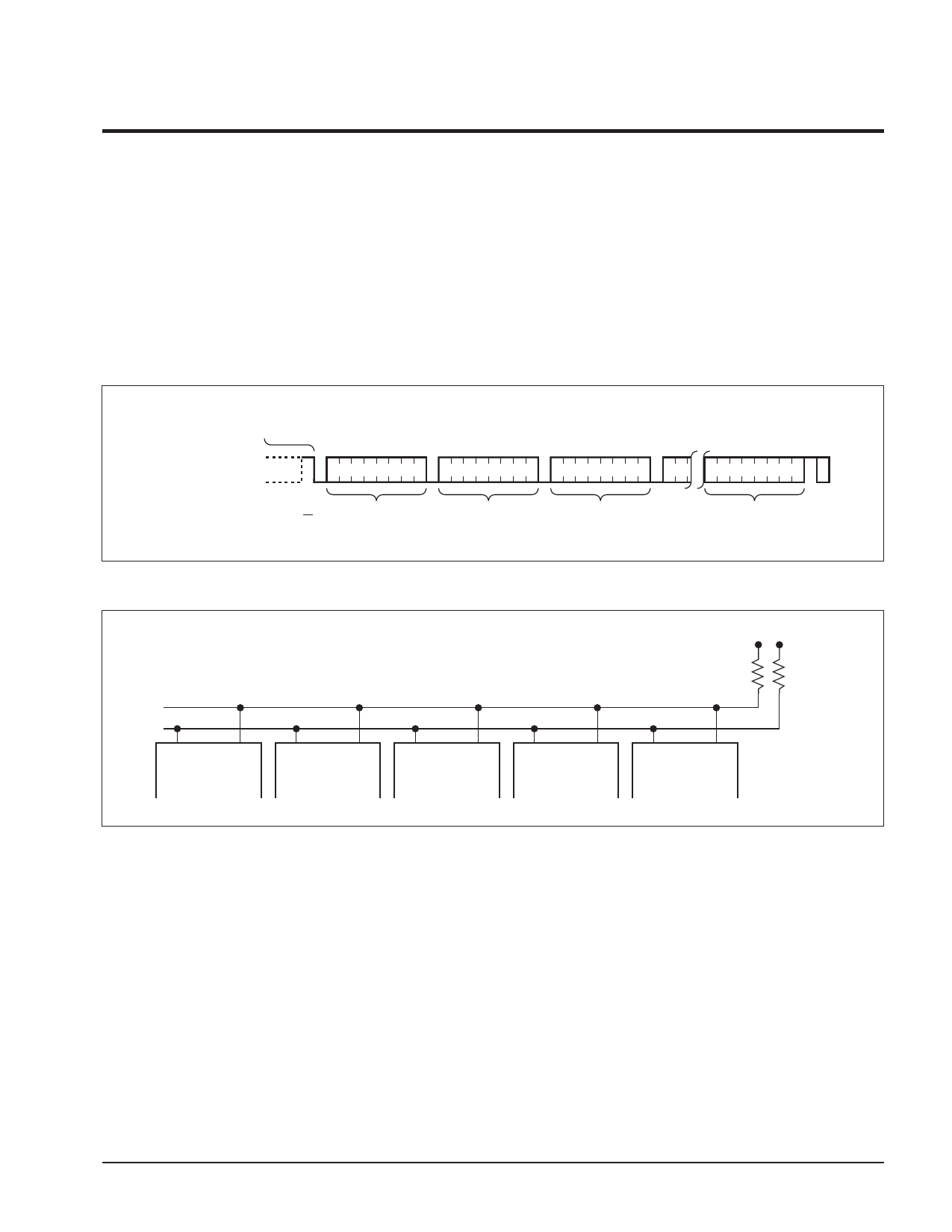

Figure 8. Sequential Read

BUS ACTIVITY: ADDRESS

SDA LINE

RA

BUS ACTIVITY:

X24C01

/C

WK

DATA n

A

A

A

C

C

C

K

K

K

DATA n+1

DATA n+2

S

T

O

P

P

DATA n+x

3837 FHD F13

Figure 9. Typical System Configuration

SDA

SCL

MASTER

TRANSMITTER/

RECEIVER

SLAVE

RECEIVER

SLAVE

TRANSMITTER/

RECEIVER

MASTER

TRANSMITTER

MASTER

TRANSMITTER/

RECEIVER

VCC

PULL-UP

RESISTORS

3837 FHD F14

7